1.前言

想在硬核上挂载一块VGA协议的TFT屏幕(5寸800*480),需要在Platform Designer中添加图像帧缓存读取控制器(Frame Reader)和VGA控制器(Clocked Video Output Intel FPGA IP)的IP核。但是17.1版本之后图像帧缓存读取控制器被整合到Frame Buffer Ⅱ (4K) Ready Intel FPGA IP中,使用这个IP核时需要修改参数,但是最后综合完之后会发现这个IP核需要另外的License,否则生成的 *.sof 文件无法使用。早说啊,真坑。

明明旧版本的Frame Reader是不需要License的啊。看来只能从早期版本的Quartus中把这个Frame Reader IP抠出来添加到新版本里了。找了半天发现其实新版本Quartus的安装路径下就有Frame Reader的IP核文件。路径为”..\intelFPGA\18.1\ip\altera\frame_reader\full_ip”。这里边会有一个“Frame Reader”的文件夹,就是这个IP核所需的文件。接下来就要将他添加到Platform Designer中去。

- 开发环境:Quartus Prime Standard Edition 18.1

- 系统版本:Windows 10 Pro x64 1809

2.添加Frame Reader IP核到Platform Designer

其实看过我另一篇文章《自定义数码管IP核,并让NiosⅡ SBT for Eclipse自动抓取驱动文件》基本就知道怎么添加了。

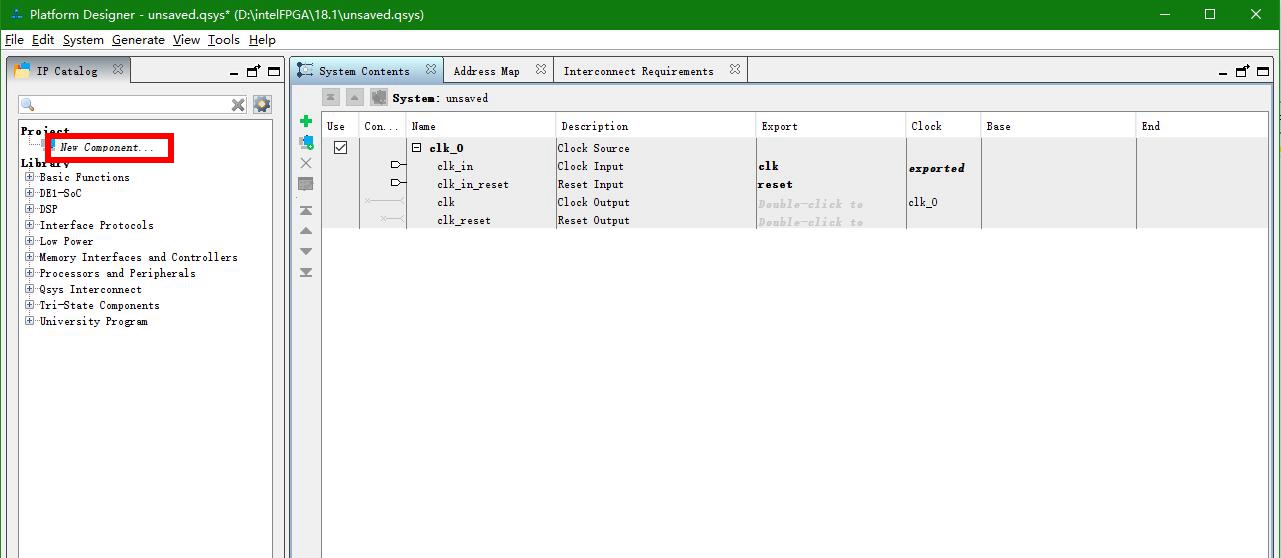

打开Quartus Prime,打开Platform Designer,直接点击IP核目录下Project里的“New Component…”。

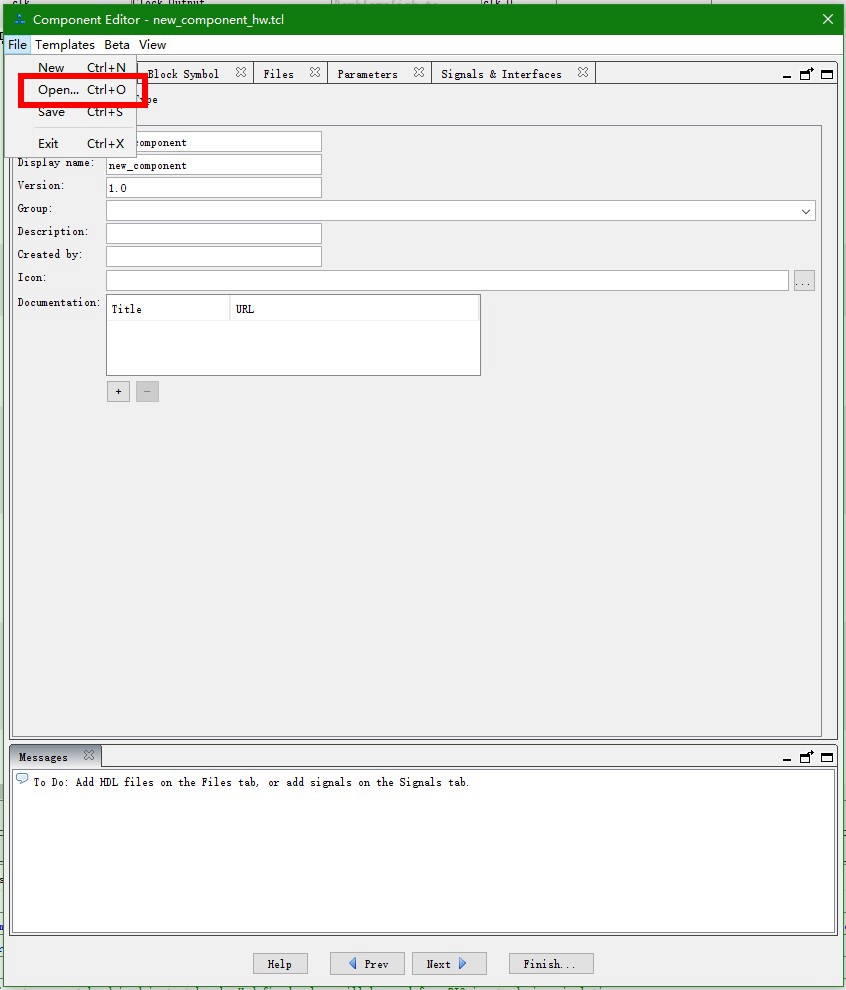

打开文件。

找到刚才提到的Frame Reader IP路径下的*.tcl文件,打开它。

不用返回去看路径了,这儿也有

"..\intelFPGA\18.1\ip\altera\frame_reader\full_ip"

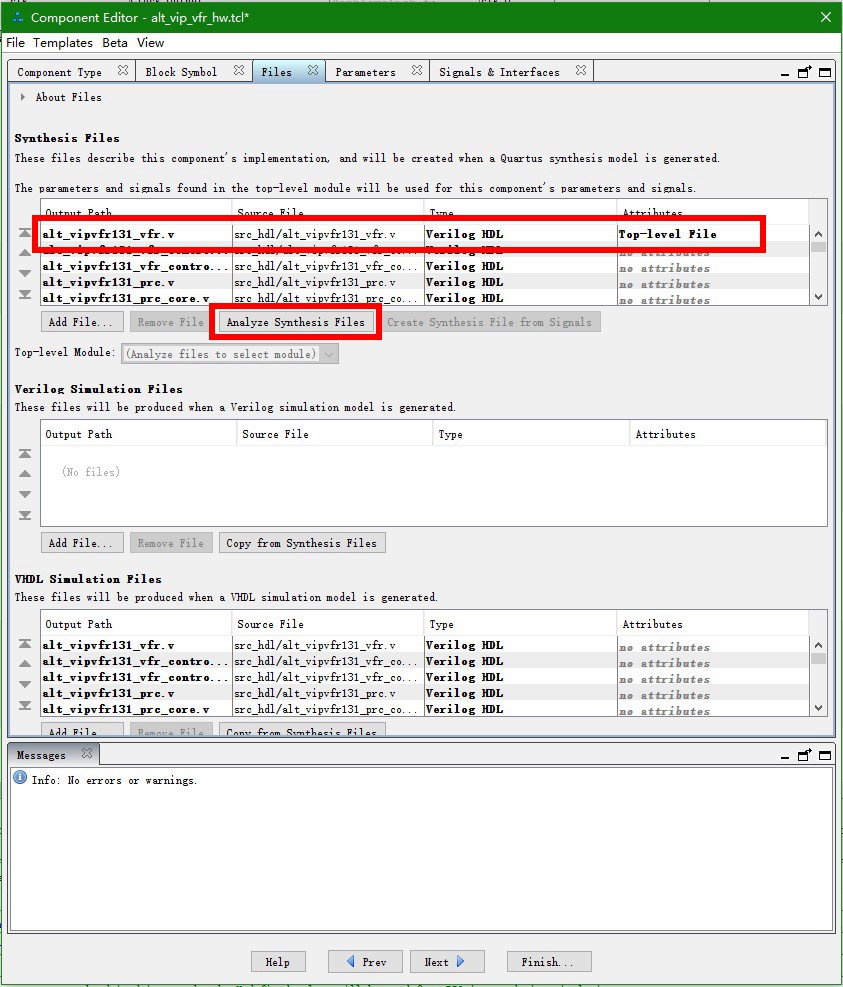

将“alt_vipvfr131_vfr.v”设置成顶层文件,然后分析。

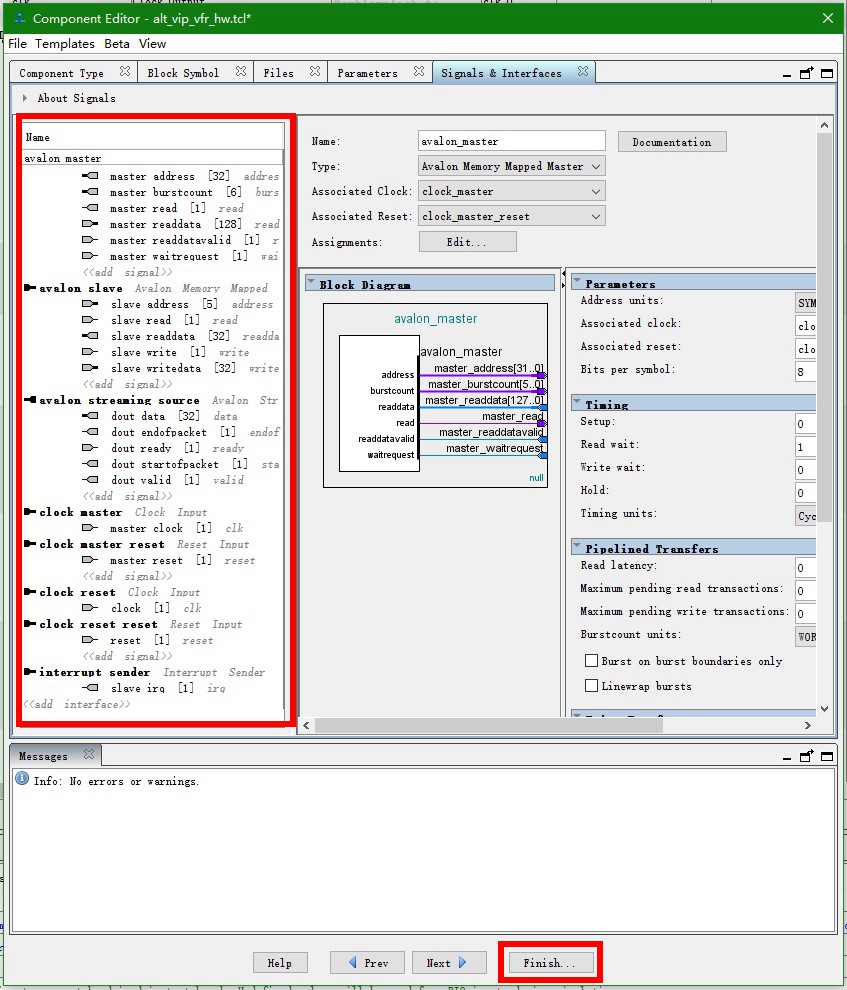

将信号修改成下图的模式,并且为总线添加时钟和复位信号。遇到错误时按照Message中的提示修改就行。最后“Finish”。

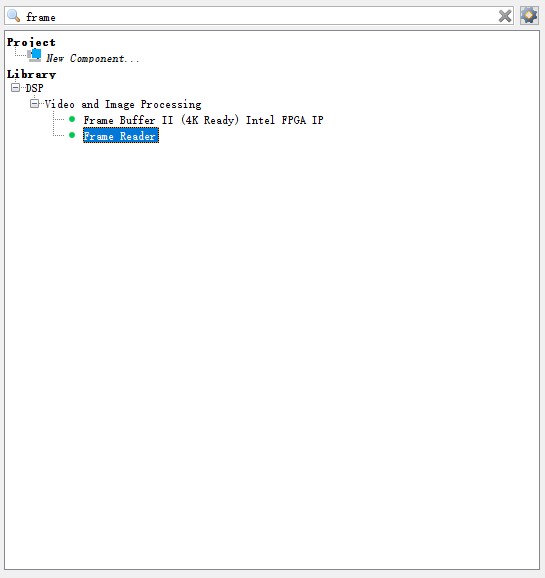

这样就将旧版中的Frame Read IP添加到新版本的Platform Designer中了。在IP核列表中可以看到它。

至于如何使用Frame Reader IP,可以参考小梅哥的SoC教程。

告辞。