硬件算法之并行计算和Flynn分类

18 Jul 2019 1209字 5分 次 Hardware Algorithm打赏作者 CC BY 4.0 (除特别声明或转载文章外)

1 Flynn分类

高性能硬件设计必须要考虑计算的并行性。有个外国人儿在1965年就提出了一种并行计算架构分类方法,因为ta叫Flynn,所以这个方法叫做Flynn分类。通用计算机架构中存在用于控制的指令流(instruction stream)和作为运算对象的数据流(data stream),Flynn分类根据基于指令流和数据流的并行度对架构进行分类:

- SISD

- SIMD

- MISD

- MIMD

该分类的对象原本是基于指令序列的通用处理器架构,而将定义扩展到指令流后,其对更加一般化的并行计算架构研究也很有价值。

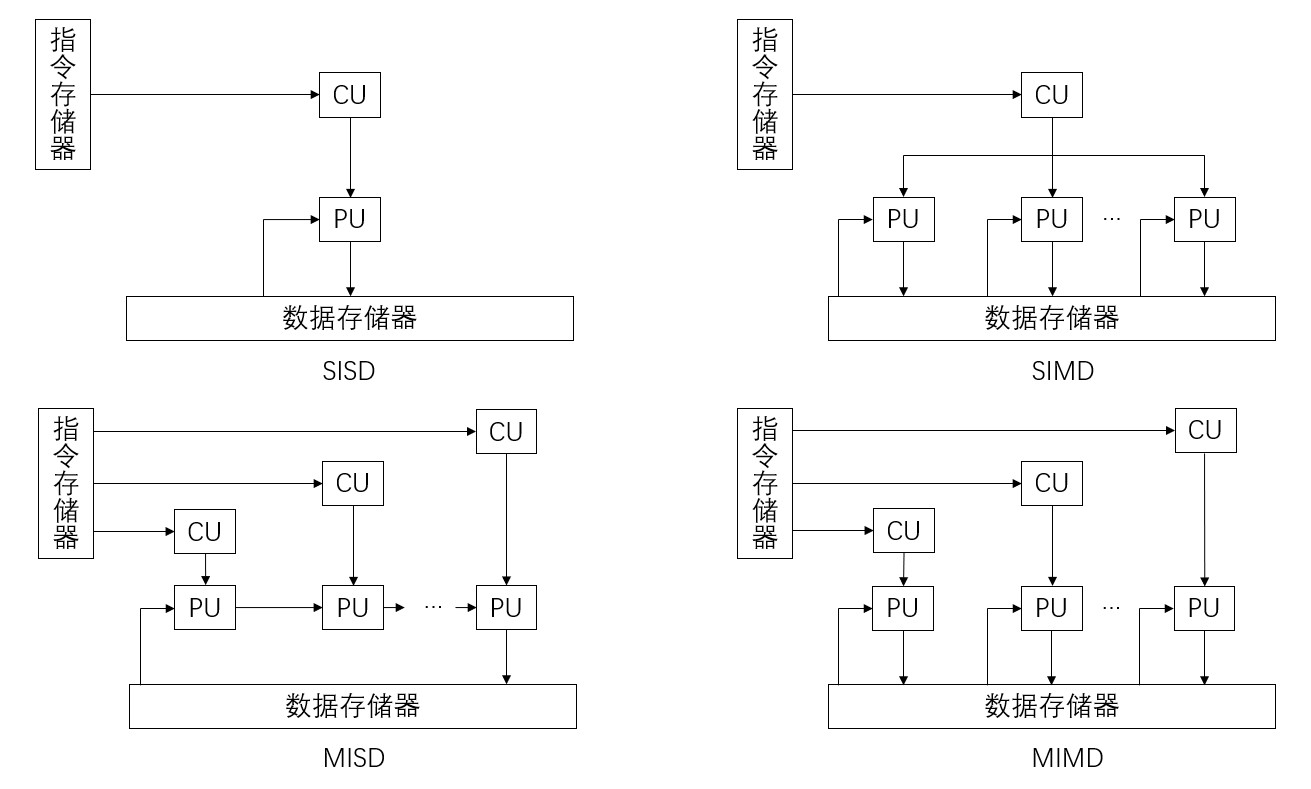

Flynn分类所使用的计算机模型由运算单元(PU)、控制单元(CU)、数据存储器、指令存储器构成。上图的SISD架构中,单一CU从指令存储器读取指令流来控制单一的PU。PU受CU控制,从数据存储器读取单一数据流进行计算处理。SISD架构代表的是按顺序计算的处理器架构,不具备并行计算能力。

2 SIMD架构

上图所示的SIMD架构中,单一CU在读取指令流的同时控制多个PU。各个PU接受相同的控制,各自对不同的数据流进行相同的计算处理。因此SIMD架构是一种具有数据并行性的架构。各个PU可以有自己的本地存储器,也可以所有PU访问同一个共享存储器。这种架构中的PU可以按照相同的指令序列同步处理大量数据,因此通常被应用在图像处理等专用处理器中。

微处理器通常还会提供SIMD指令来实现数据的并行计算。因此使用SIMD扩展指令集是实现微处理器性能最大化的必要条件。

3 MISD架构

上图所示的MISD架构中,多个CU各自读取不同的指令流并控制多个PU。各个PU根据不同的控制指令对单一数据流进行操作。现实中很难找到属于这一分类的通用微处理器,不过如果将一系列PU视为流水线的阶段,每个阶段各自独立可控,这样组成的粗颗粒度的流水线结构就可被认为是MISD架构。通过每个CU各自控制一个不同功能的PU来实现并行计算,因此MISD架构是一种具有功能并行性的架构。例如在一个面向图像处理的处理器阵列中,多个连续的阶段分别依次进行像素转换、边缘检测、分类等操作,每个阶段分别由独自的指令集控制,这就可以归类为面向特定用途的MISD架构。

4 MIMD架构

上图所示的MIMD架构中,多个CU各自读取不同的指令流并控制多个PU。然而和MISD架构不同的是,各个独立受控的PU对不同的数据流并行处理。因此MIMD架构是一种同时具有数据并行性和功能并行性的架构,可以实现多个指令序列操作多个数据。例如SMP(Symmetric Multi-Processor)等多个核心紧密结合的处理器,其中多个微处理器或位处理器核心共享存储系统,可以归类为数据存储器共享型MIMD架构。另外,各个计算节点拥有独立的处理器和局部存储器,通过互联网络相连的计算机集群,可以归类为数据存储器独立的MIMD架构。

告辞。