时序约束之综合

13 Sep 2019 1166字 4分 次 Digital IC Design Tcl打赏作者 CC BY 4.0 (除特别声明或转载文章外)

1 前言

在使用时序约束的设计过程中,综合(Synthesis)是第一步。

2 综合的定义

在电子设计中,综合是指完成特定功能的门级网表的实现。

其实就是把HDL代码变成RTL电路。通常仅仅是指逻辑综合。

3 时序约束在综合中的作用

3.1 优化

在设计中,面积、功率和性能是三个重要指标,但往往不能兼得。而约束文件可以告诉综合工具侧重哪一方面进行综合。

3.2 输入重排序

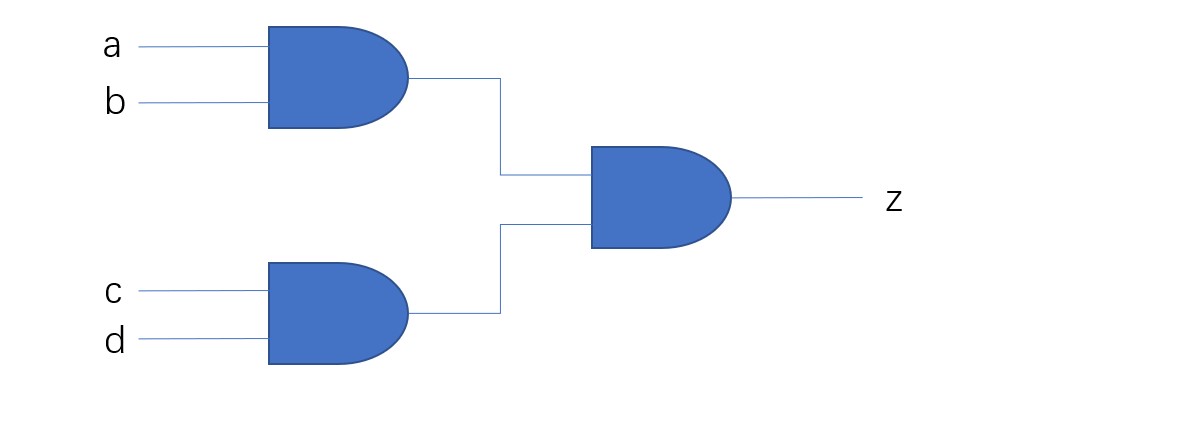

假设有四输入a、b、c、d进行“与”操作,电路实现如下图:

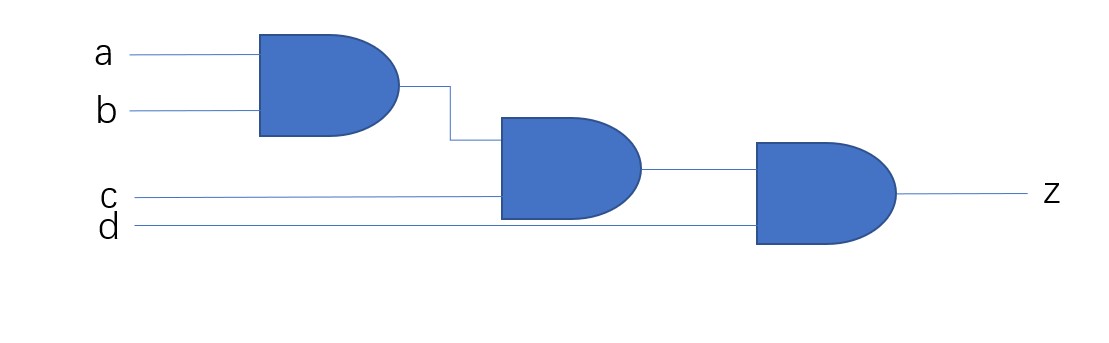

如果输入d来得比其他三个输入晚,该电路输出必须等到d达到并通过两个与门才能实现。所以通过以下电路修改实现:

在该电路中,等到d到达时,其他三个信号已经被使用,而d只需要通过一个与门。

虽然两个电路执行相同的功能并具有相似的面积(三个与门),但在该条件下显然第二种电路更符合要求。

约束文件可以告诉综合工具每种输入信号到达的时间,综合工具根据这个使得最后到达的信号必须通过最少的逻辑电路。

3.3 输入缓冲

约束文件需要告诉综合工具驱动外部输入信号的驱动能力,以便综合工具约定是否放置额外的缓冲器。

3.4 输出缓冲

与输入缓冲类似。

4 综合中面临的问题

4.1 设计划分

综合工具最大的瓶颈是他可综合设计的规模。与综合工具可以综合的设计规模相比,当今的设计规模是巨大的。因此,一个完整的设计必须被拆分成更小的单元,称之为单元电路(block)。综合工具将一个电路单元综合为一个单位,因此,综合工具在任何给定时间仅能查看一个单元电路,并且看不到电路单元如何与设计的其余部分进行交互。

在任何时刻,综合工具都可以查看一个电路单元,同时他对完整设计的要求是已知的,因此完整设计的顶层约束必须分解为各个电路单元的约束。对于各个电路单元,这些约束必须给予这个电路单元与所有其它电路单元的交互来创建。

所以,本应只在顶层的约束线在被转换成在每个接口定义的更多约束。而随着约束数量的增加,错误概率也随之增加。

4.2 更新约束

假设电路单元A不满足时序要求,这些时序会影响B。电路单元B的设计者现在必须更新其约束,并且可能影响其他接口,但是这些接口的约束可能与B更新的约束不同步,而且在许多情况下,这些改变的约束可能干扰面积、性能和功率之间的微妙平衡。因此,电路单元级约束可能必须根据电路单元如何集成在子系统或芯片中来更新。

4.3 多时钟设计

目前大多数设计具有多个处理器核,运行在不同的时钟频率,这些核可能有不同的外设。这些核是由多个设计组同时开发的,在集成它们的过程中,在初步实现期间可能会忽略用低频约束来约束高频核的无意错误。这些错误可能最终会在全芯片STA和后综合期间遇到,所以现在必须重新搭建电路单元约束以符合最初的设计规格,这将引起在芯片综合中增加了不必要的反复,这有可能会非常慢。

告辞。