时序约束之生成时钟

23 Sep 2019 2439字 9分 次 Digital IC Design Tcl打赏作者 CC BY 4.0 (除特别声明或转载文章外)

1 前言

复杂的设计需要多个时钟。如果有多个时钟源,即异步时钟,它们之间是不能共享确定相位关系的。当多个时钟域交互时,设计中只有异步时钟很难满足建立和保持要求。所以通常多个时钟都源于一个主时钟,即生成时钟。这种时钟可以通过以下几种方式产生:

- 时钟分频器;

- 时钟乘法器;

- 时钟门控。

2 时钟分频器

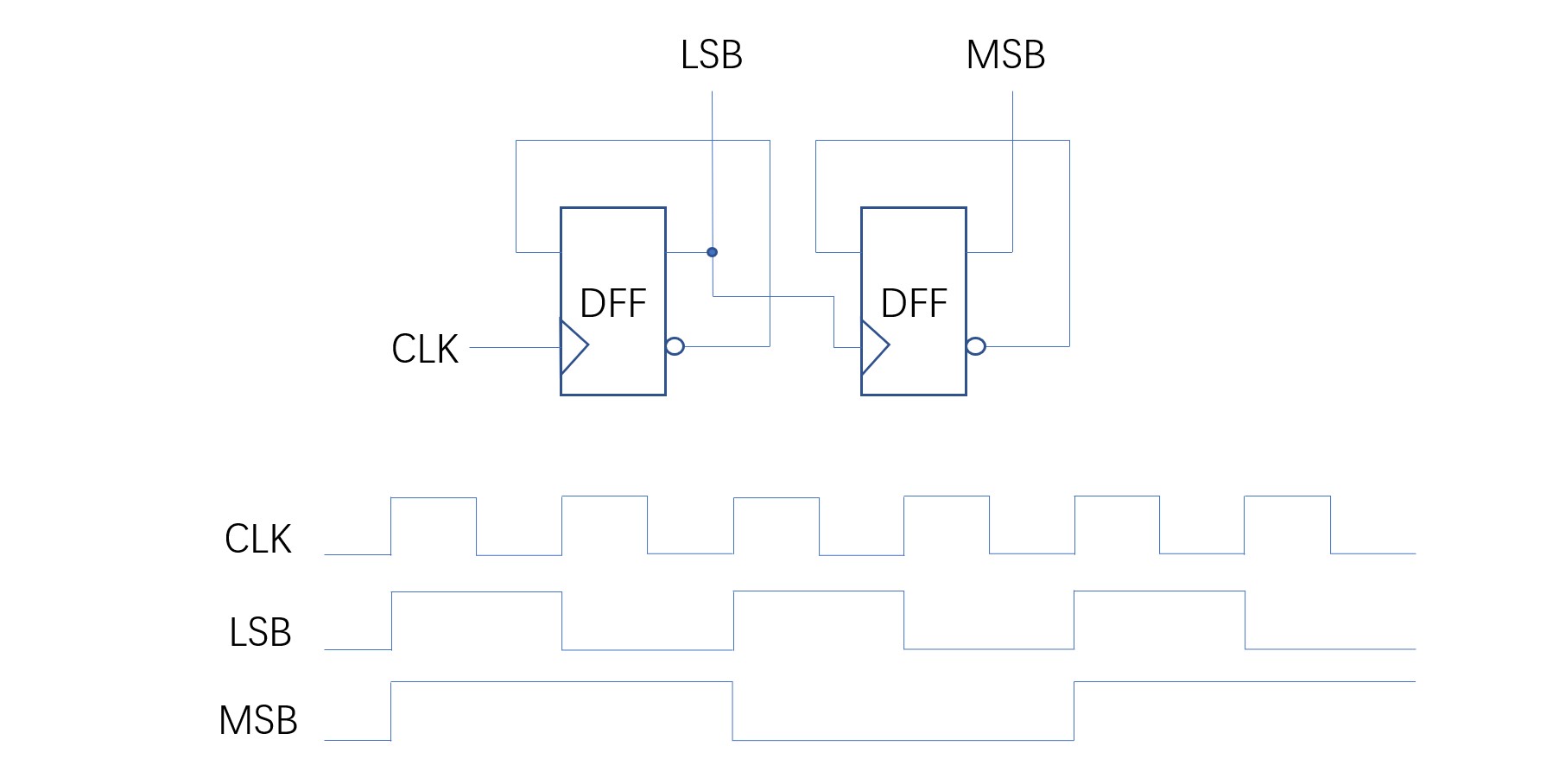

时钟分频器产生一个比原始时钟源频率更低且周期更长的时钟信号。典型的时钟分频器是2位纹波计数器。纹波计数器的电路图如图所示:

对于该电路,如果第一个输入触发器的时钟周期为10ns,则在产生波形的LSB除以2,得到周期为20ns的信号。同样,在波形的MSB除以4,则可以得到周期为40ns的信号。

3 时钟乘法器

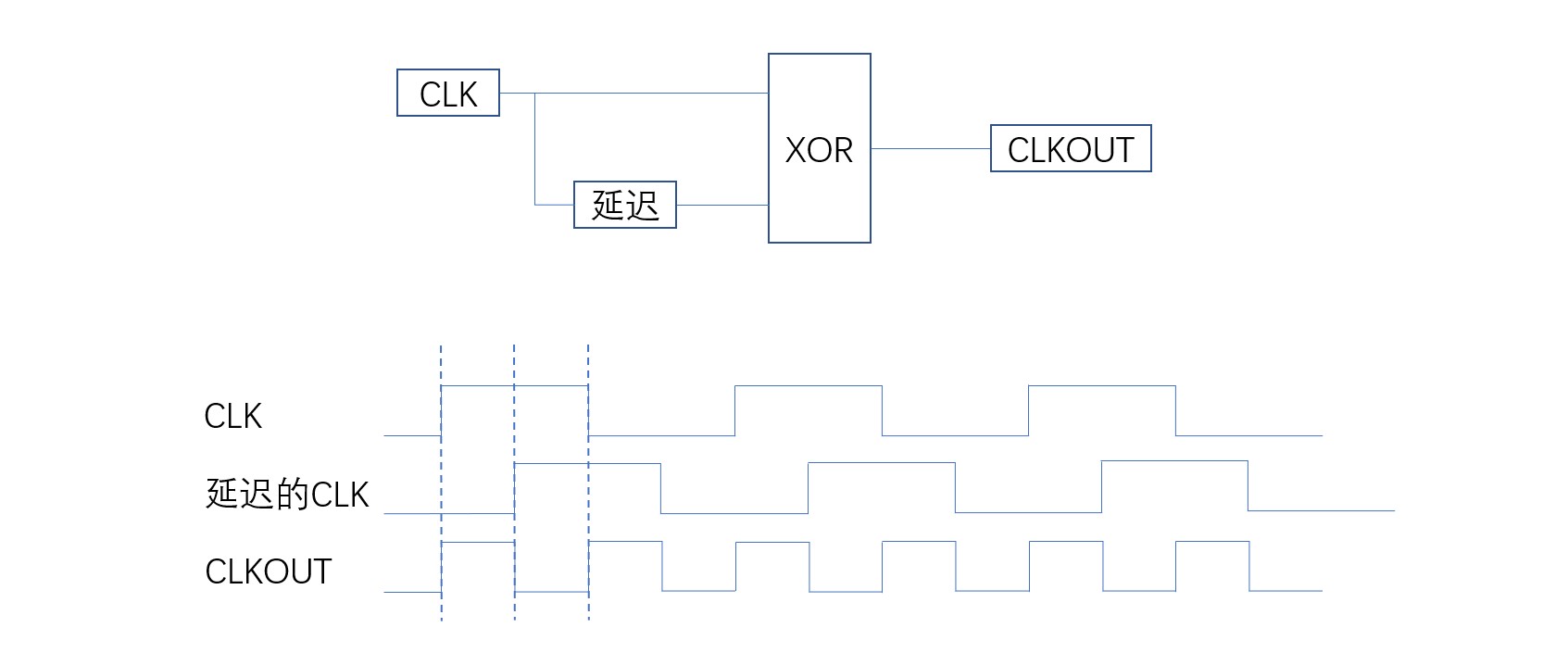

时钟乘法器是一种通过频率增加和周期减少来获得更快时钟速度的电路。下图为一个简单的实现时钟倍频的时钟乘法器电路。该电路实现了时钟信号的产生以及具有延迟的功能。延时可用过缓冲器和反相器引入到线路中:

通常利用PLL来实现倍频。

4 时钟门控

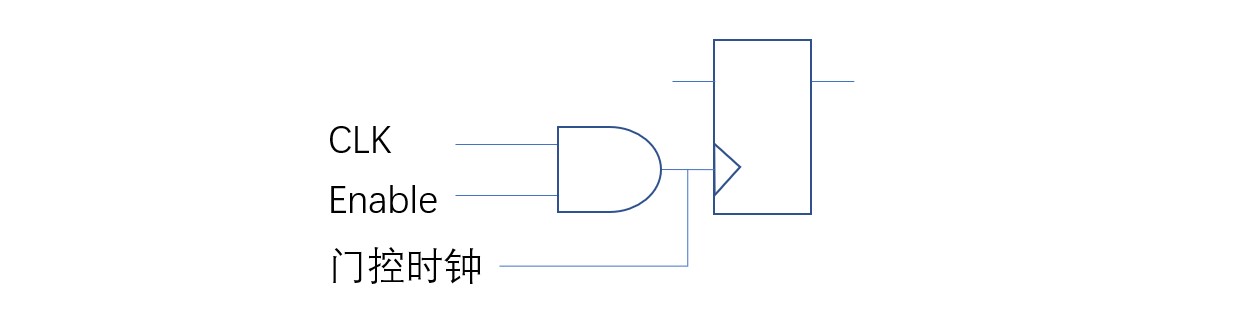

自20世纪90年代中期以来,时钟门控成为了一种非常流行的减少功耗的技术。当触发器或寄存器因时钟触发而改变状态时,会产生一定的功耗。然而部分逻辑电路可能又不会在某些时候派上用场。这种情况下禁用这部分时钟信号可以减少状态切换带来的功耗。也就是说时钟信号要等到逻辑电路使能之后才有效。这种时钟称为门控时钟。下图为门控时钟示例:

5 create_generated_clock

SDC指令中用于设定生成时钟的命令是“create_generated_clock”。该指令的BNF为:

create_generated_clock [source_objects]

-source clock_source_pin

[-master_clock master_clock_name]

[-name gennrated_clock_name]

[-edges edge_list]

[-divide_by factor]

[-multiply_by factor]

[-invert]

[-edge_shift shift_list]

[-duty_cycle percent]

[-combinational]

[-add]

[-comment comment_string]

5.1 定义生成时钟的对象

与“create_clock”相似。

5.2 定义生成时钟的源

与时序约束之时钟中的4.2类似。

5.3 时钟命名

与时序约束之时钟中的4.3类似。

5.4 设定生成时钟的特性

设定生成时钟的特性可以利用以下三个选项当中的一个:

- -edge:与时序约束之时钟中的4.4类似;

- -divide_by:这表示生成时钟通过某个因子而分频,周期加倍;

- -multiply_by:这表示生成时钟通过某个因子而倍频,周期要除以这个因子。

5.5 时钟沿位移

生成时钟的时钟沿可能受时间的影响发生位移。例如:

create_generated_clock -name PULSE

-source [get_ports clk]

-edges {1 1 3}

-edge_shift{0 2 0} [get_pins AN1/Z]

“-edge_shift”选项选取一组浮点数来表示在单元时间内每一个时钟沿的位移。该选项必须具有与时钟沿数量相同的参数来表示每一个生成时钟沿的位移。

位移可以是正向也可以是反向,利用“-edges”和“-edge_shift”可以对任何复杂的生成时钟进行建模。

5.6 多个同源时钟

与时序约束之时钟中的4.5类似。

5.7 使能组合电路路径

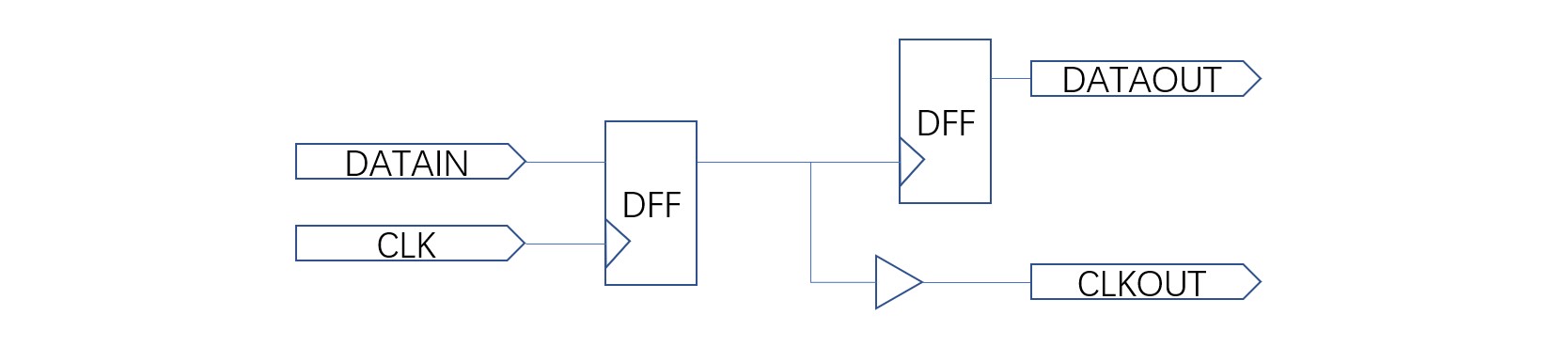

下图给出了一个源同步接口:

在源同步接口中,时钟随着数据作为输出。这种结构的优点是时钟和数据按同样的路径来传输,因此他们具有相同的延迟,接收设备可以根据输入时钟对输入数据进行采样。只有两条线路的延迟差接近0,那么实际线路的延迟并不重要。这种结构提供了一个高速数据传输的接口。

上图中DATAOUT引脚的延迟应当根据CLKOUT设定。这种情况下,生成时钟需要定义在CLKOUT上,这可利用“-combinational”选项实现。设定了该选项后,生成时钟与主时钟引脚的周期相同,相当于“divide_by 1”。这时不可用其他任何选项,其表示为:

create_generated_clock -name CLKOUT -comninational

-source [get_pins FF1/Q][get_ports CLKOUT]

在某些情况下,从源时钟引脚到定义的生成时钟可能有多个路径。如果这些路径在本质上是时序电路,即它们通过触发器这类的时序电路元件或透明的锁存器,则利用常用方法定义的生成时钟一般是无损的。然而某些情况下,如果从源引脚到生成时钟的路径是纯组合电路,有同时存在时序电路,则利用常用的定义方法“create_generated_clock”将会失效。在这种情况下,租个时序电路是非常重要的,因为组合电路始终有效。也就是说,通过“-combinational”选项定义的生成时钟已经生效了。

6 生成时钟相关的注意事项

由于时钟可由多种方式生成,所以这通常会造成设计功能遇事需规范之间不匹配。对于设定生成时钟,设计者必须注意以下几点:

- 如果定义一个时钟,应确保其是由特定源对象所生成的,不过,如果触发器或寄存器是有另一个时钟扇出的时钟信号驱动的,则要确保设定了“create_generated_clock”相关的约束,一个遗漏的生成时钟将会产生无约束寄存器;

- 当多个时钟收敛于一个时钟源引脚时,应确保在定义生成时钟时设定了主时钟;

- 如果在一个引脚上存在多个源,需要设定多个生成时钟约束,应确保使用“-add”选项,否则最新设定的约束会覆盖掉其他的约束;

- 避免时钟收敛于多个组合电路路径,否则可能会导致脉冲,如果时钟收敛于多种路径(组合电路和时序电路),则特别要注意禁用时序电路路径。

告辞。