时序约束练习

18 Oct 2019 822字 3分 次 Digital IC Design打赏作者 CC BY 4.0 (除特别声明或转载文章外)

1 前言

看了点时序约束的书,白嫖了小梅哥的时序约束教程,是时候上手了。

- 开发环境:

- Quartus Prime Standard 18.1

- 操作系统:

- Windows 10 Pro 1903

2 计数器约束与优化

一个很简单的计数器,约束之前是这样写的:

parameter ts = 26'd20; //计时周期

reg [25:0] cnt_s;

always@(posedge clk or negedge rst_n) begin

if(!rst_n)

cnt_s <= 26'b0;

else if(cnt_s < ts)

cnt_s <= cnt_s + 1'b1;

else

cnt_s <= 26'b0;

end

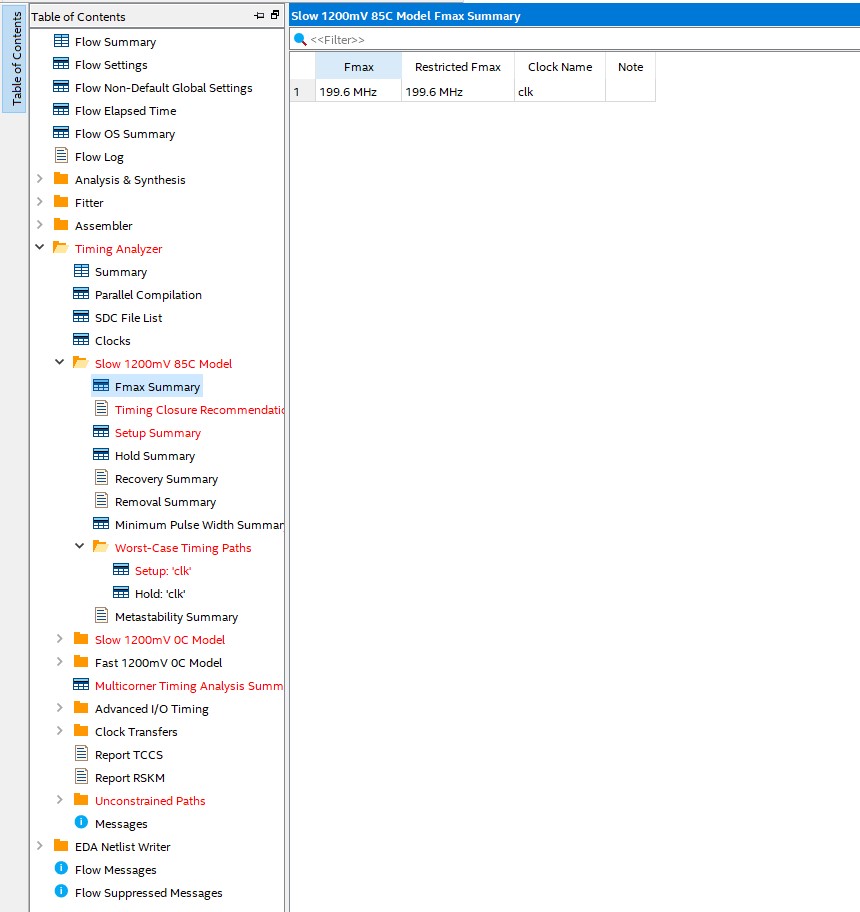

然后编译,写约束文件。再重新编译,在“Complilation Report”的“Timing Analyzer”->“Slow 1200mV 85C Model”->“Fmax Summary”中可以看到最大时钟频率为199.6MHz:

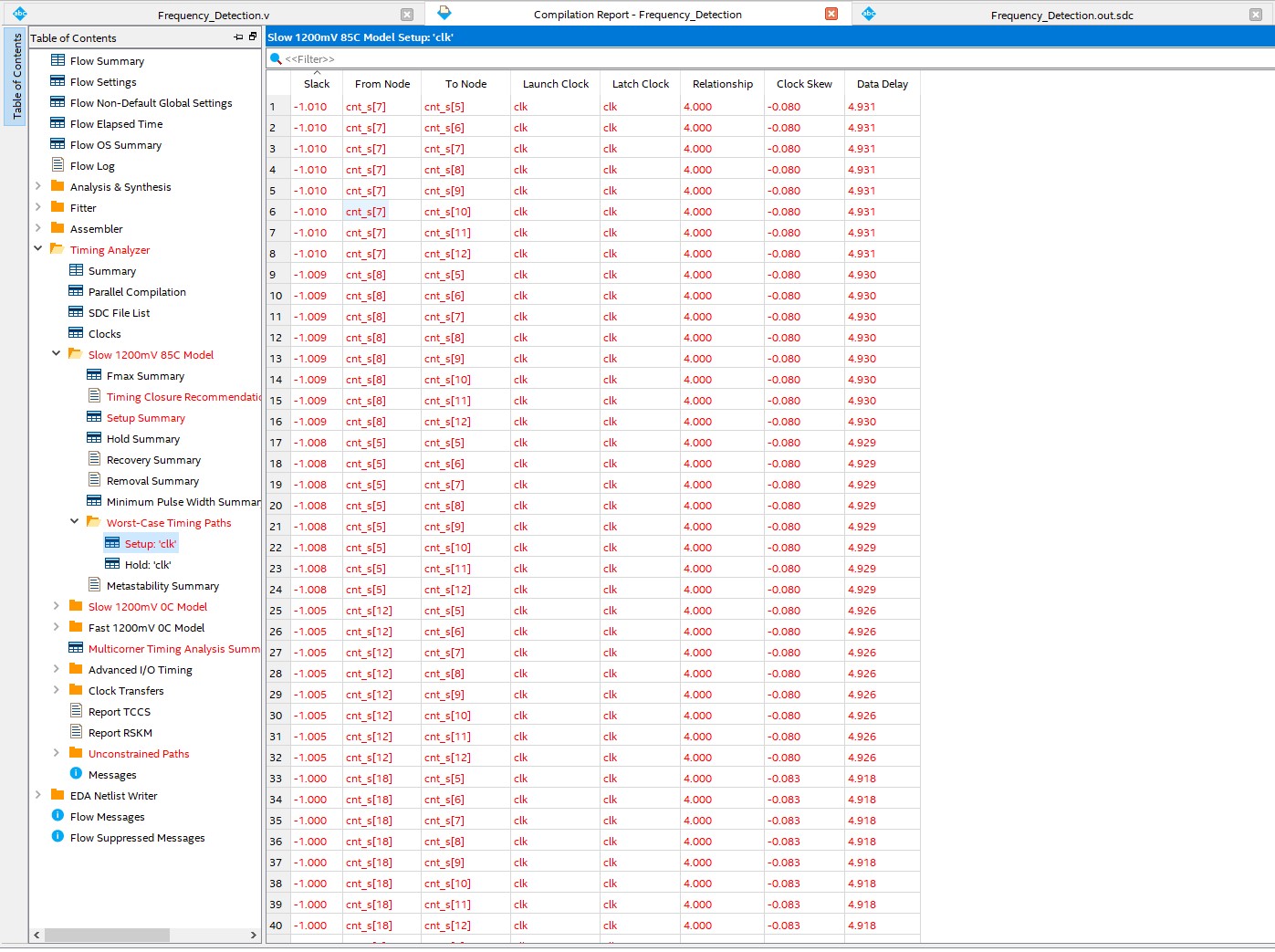

再在“Worst-Case Timing Paths”->“Setup:‘clk’”中看最差路径:

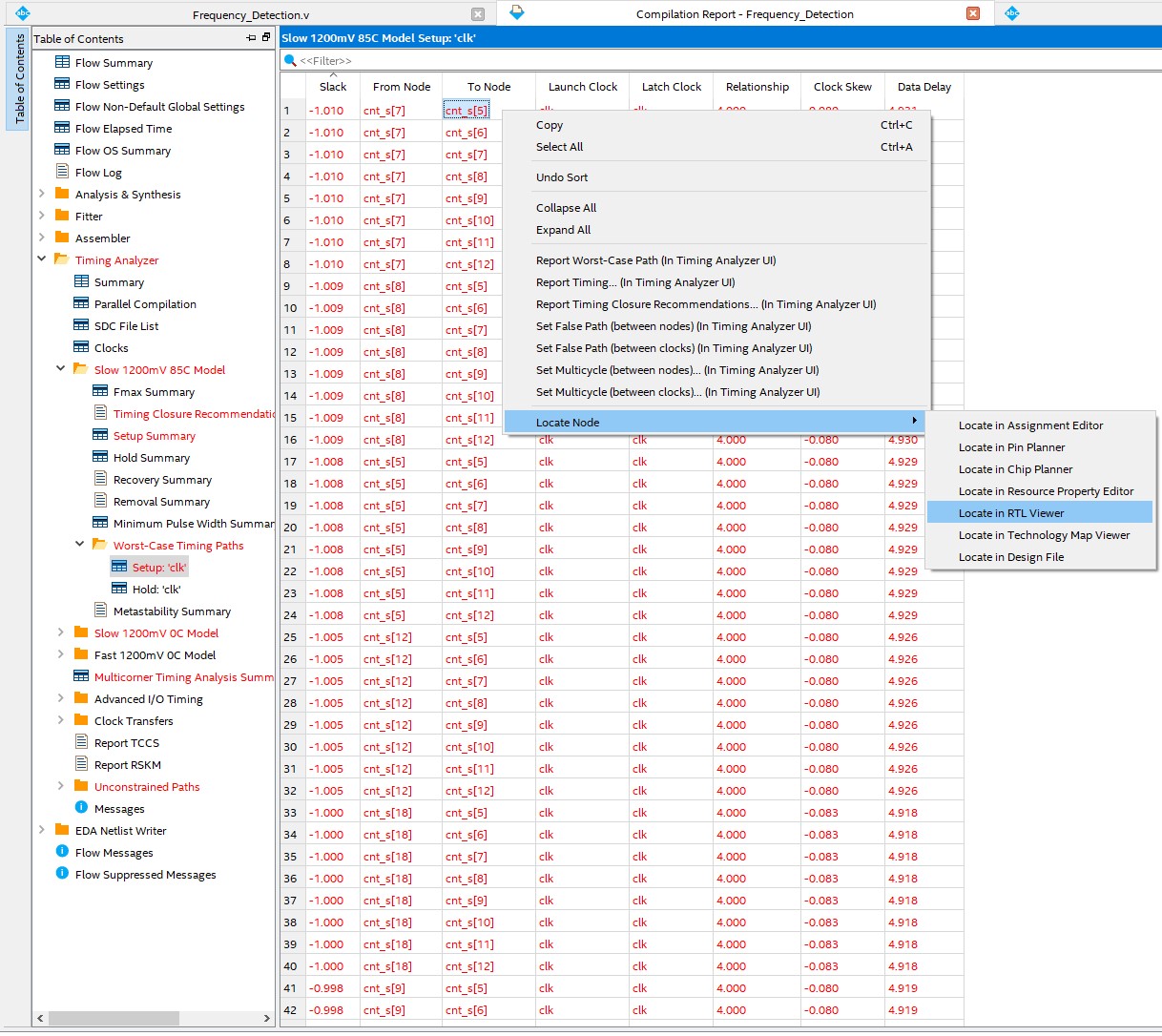

可以看出最差的是计数器这一堆,点右键看一下RTL:

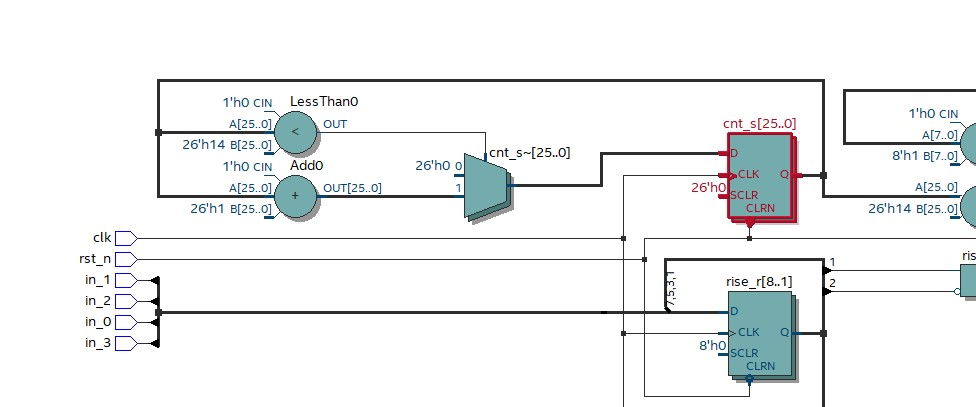

计数器的RTL如下图:

也不知道咋的,就把HDL改成下面这样子:

parameter ts = 26'd20; //计时周期

reg [25:0] cnt_s;

always@(posedge clk or negedge rst_n) begin

if(!rst_n)

cnt_s <= 26'b0;

else if(cnt_s == ts)

cnt_s <= 26'b0;

else

cnt_s <= cnt_s + 1'b1;

end

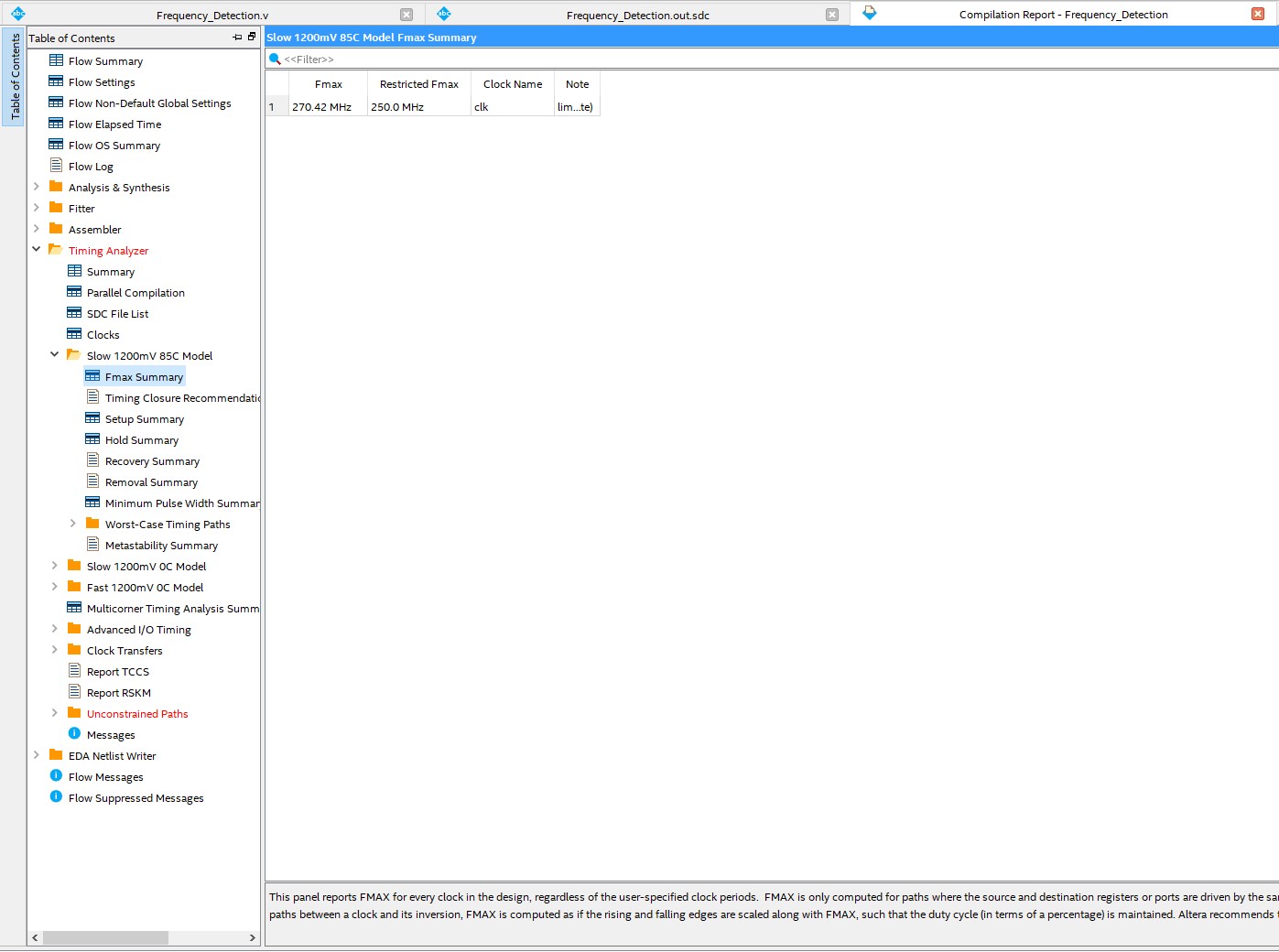

再来一遍时序分析,可以看到最大时钟频率变成了270MHz:

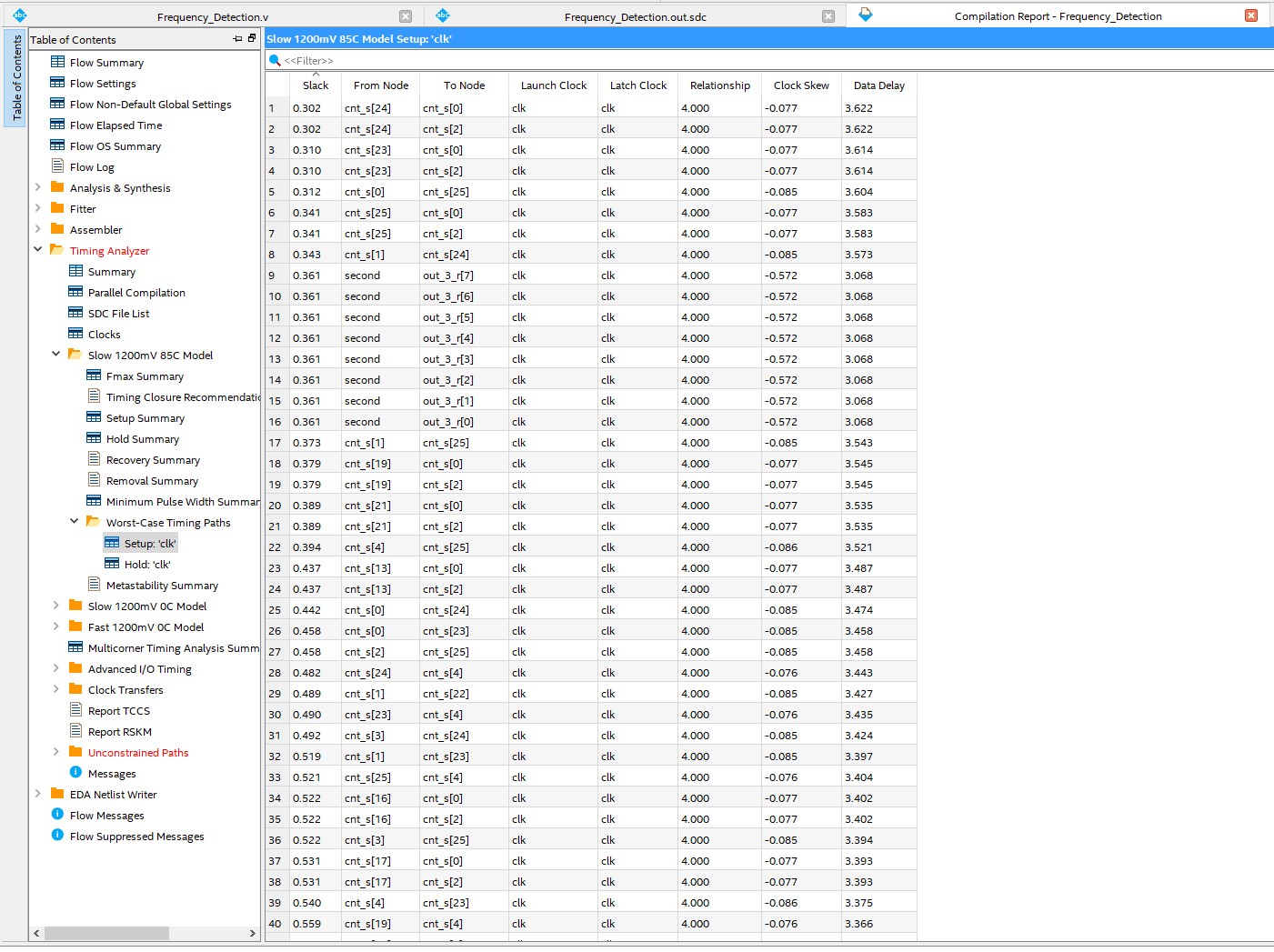

最坏路径的建立时间最小变成了0.302:

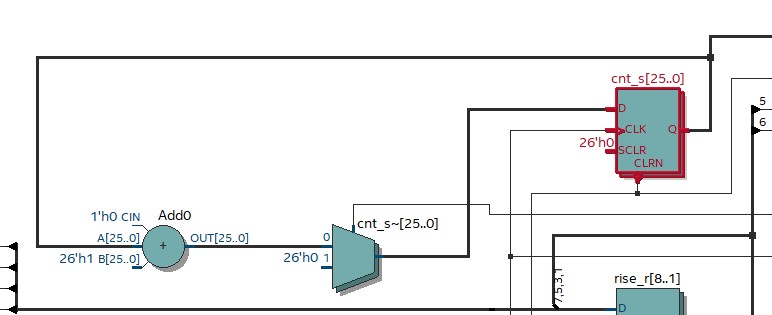

RTL图变成了如下这样:

可以看出少了一个加法器。

告辞。