1 前言

本文根据官网中文视频教程采用Altera收发器器件进行高速串行协议设计总结。

- 开发环境:

- Quartus Prime Standard 18.1

- 操作系统:

- Windows 10 Pro 1909

2

2.1 Altera收发器器件介绍

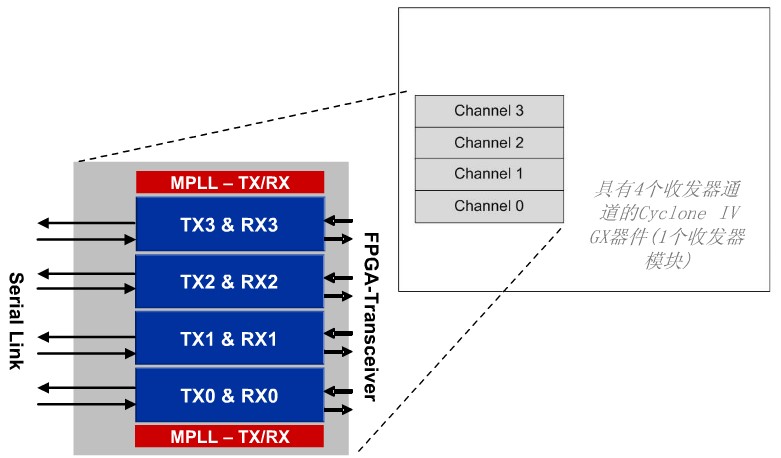

Intel PSG的FPGA中只要带GX的都支持定制协议的收发器,Cyclone IV GX系列收发器模块体系结构如下图:

可以看出有四个完整的收发通道,速度可以达到3.125Gbps。

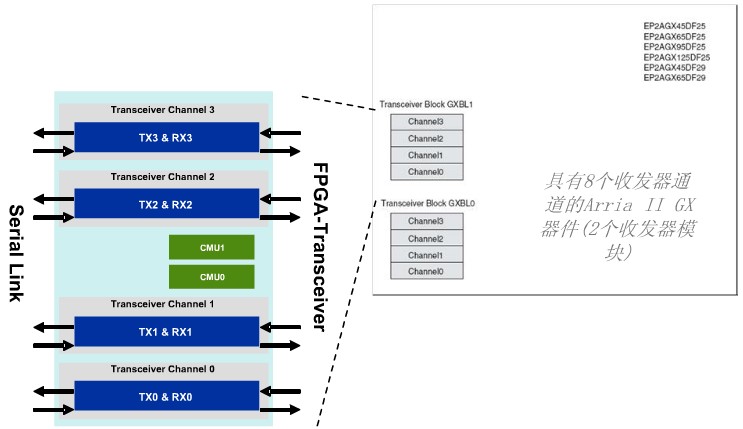

Arria II GX/GZ系列收发器模块体系结构如下图:

可以看出有八个完整的收发通道,速度可以达到6Gbps。

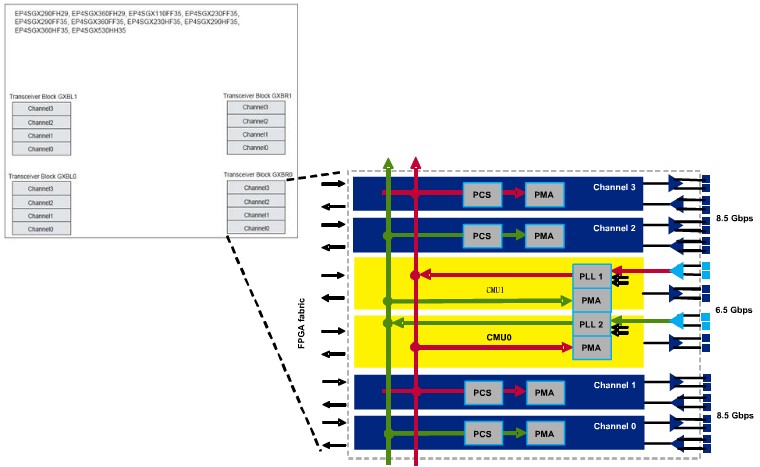

Stratix IV GX/GT系列收发器模块体系结构如下图:

可以看出有十六个完整的收发通道,速度最多可以达到8.5Gbps。

Stratix V GX/GS系列收发器模块体系结构如下图:

可以看出有二十四个完整的收发通道,速度可以达到12.5Gbps。

3 嵌入式收发器介绍

3.1 收发器结构

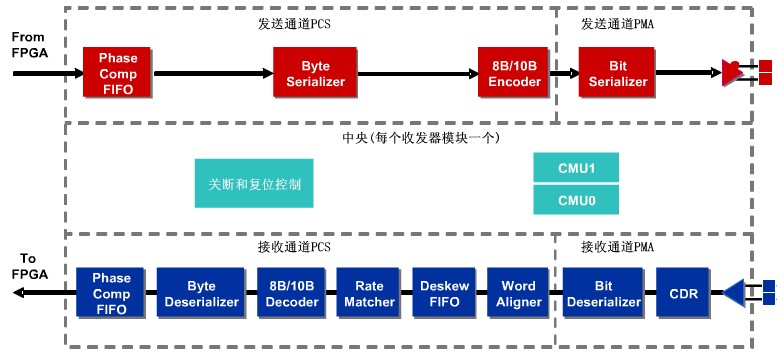

嵌入式收发器结构如下图所示:

左侧为FPGA逻辑,右侧为收发器I/O。

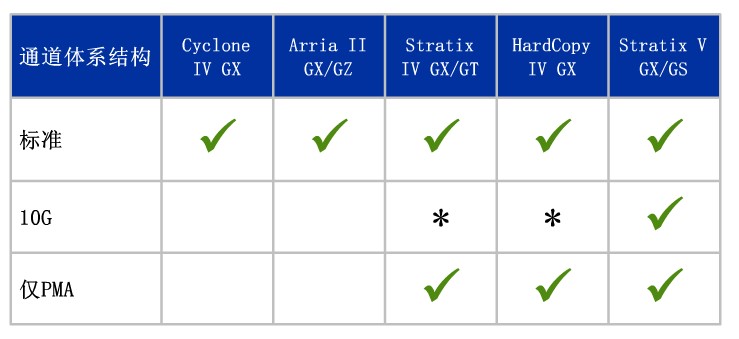

3.2 器件、通道体系结构

收发器由三个通道构成:

- 标准通道;

- 10G通道;

- 仅PMA通道。

它们所支持的器件如下表:

这些器件中的收发器不能直接支持10G体系结构。

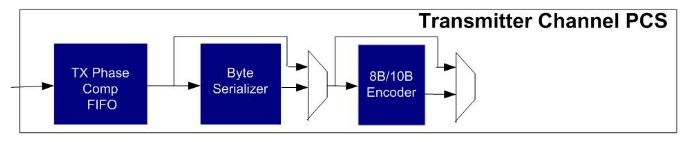

4 标准收发器通道体系结构

4.1 发送器通路

发送器通路由已下三部分组成:

- 发送器相位补偿FIFO;

- 字节串化器;

- 8B/10B编码器。

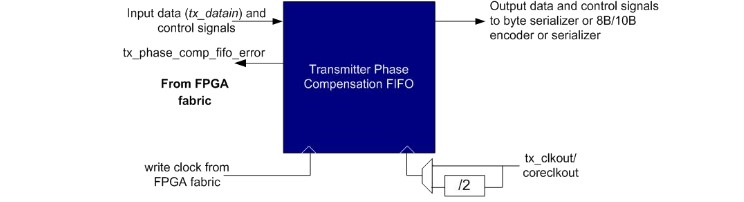

发送器相位补偿FIFO将两个时钟域之间的相位失调进行去耦合,确保FPGA架构和发送器PCS(物理编码子层)之可靠的数据传送。写时钟和读时钟之间需要0 PPM相位差。

当FIFO上溢或下溢时置位,指出发送了不可靠的数据。

发送器相位补偿FIFO支持非绑定和绑定模式。非绑定模式有独立的FIFO读、写指针和使能;绑定模式中所有发送器相位补偿FIFO共享同一FIFO读、写指针和使能,且控制信号共享,通过所有绑定通道FIFO具有相同的不确定性延时,从而保证较低的发送器通道至通道偏移。

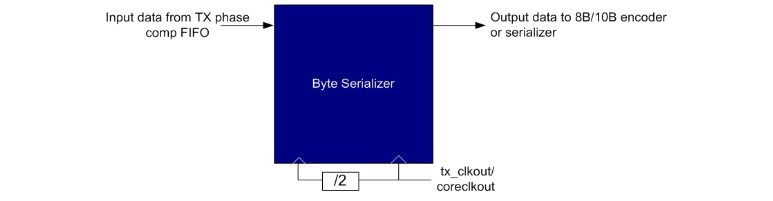

与PCS的其他部分相比,运行频率是一半时,发送器端口的宽度会加倍,当FPGA发送器接口频率高于接口最大频率时需要使用字节串化器:

字节串化器支持两种模式:

- 单位宽:

- 16/20位数据输入=>8/10位数据输出;

- 器件支持:所有器件;

- 双位宽:

- 32/40位数据输入=>16/20位数据输出;

- Arria II GX、Stratix IV GX/GT、Stratix V GX/GS等。

字节串化器模式决定通道的最大数据速率。

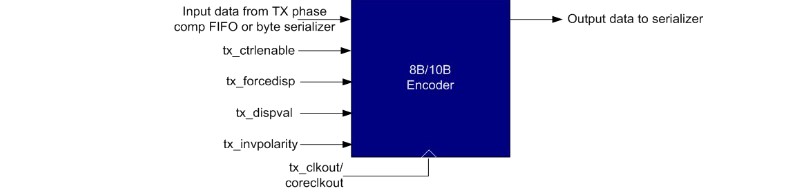

8B/10B编码器可以处理输入数据和控制信号:

- 输入信号:

- tx_datain(8位或16位输入);

- tx_ctrlenable(1位或2位输入)(设定tx_datain为被编码的数据(‘0’)或控制码(‘1’));

- 可选控制信号:

- tx_forcedisp & tx_dispval(一起使用,强制进行正或负校验);

- tx_invpolarity(对于差分走线交换的情况,‘1’翻转数据极性)。

8B/10B编码器的校验模式如下表:

| tx_forcedisp | tx_dispval | 校验 |

|---|---|---|

| 0 | X | 一般确定运行校验,上电或复位时进行负校验 |

| 1 | 0 | 强制正校验 |

| 1 | 1 | 强制负校验 |

低延时发送器PCS模式旁路所有的PCS模块,除了发送器相位补偿FIFO和字节串化器,减小了发送器数据通路延时。

发送器PMA功能模块包括串化器和TX缓冲器两部分。

串化器支持位滑动,有助于获得确定性延时。这一特性使用tx_bitslipboundaryselect[4:0]输入端口进行控制,端口上的数值决定了要滑动的比特数:

- 单位宽模式:0-9滑动bit;

- 双位宽模式:0-19滑动bit。

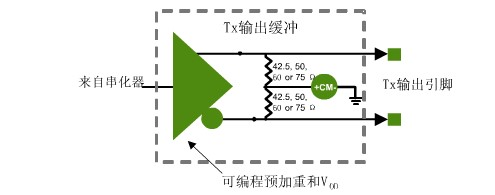

发送缓冲器可选片内匹配(OCT),支持85Ω、100Ω、120Ω和150Ω,如果禁用,则需要外部匹配。还具有可编程的Vod,电压范围为170-1350mV,取决于器件和OCT。

发送缓冲器具有可编程的预加重功能,输入驱动器电压可被设置为1.4或1.5V,具体取决与器件。

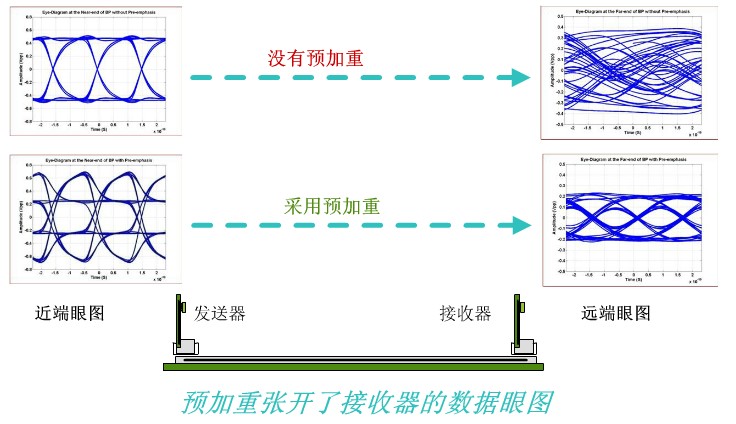

使用预加重功能可以补偿码间干扰的传输线损耗,提高了输出信号的高频分量,均衡了传输介质的线路损耗:

4.2接收器通路

接收器PMA功能模块包括:

- 接收器缓冲;

- 时钟和数据恢复(CDR)单元;

- 解串器。

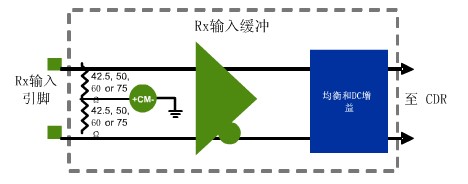

接收缓冲具有和发送缓冲一样的可编程OCT;可编程Vcm支持0.82或1.1V电压;支持AC或DC耦合,支持可编程DC增益,提升所有频率分量电压。

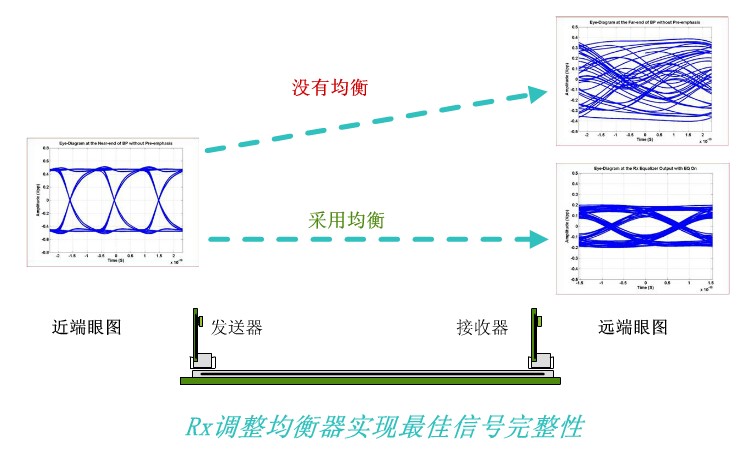

和发送器缓冲的预加重功能类似,接收器缓冲具有可编程均衡功能,提升输入信号的高频分量,补偿由于传输线低通滤波特性导致的高频损耗。

CDR从串行数据中恢复时钟,生成PCS和FPGA架构几口时钟的低速恢复时钟。每个接收通道一个专用CDR,Quartus Prime软件根据所选择的数据速率自动设置分频器。

CDR有两种工作模式:

- 锁定至参考(LTR):

- PFD跟踪输入参考时钟;

- 用于训练CDR;

- 锁定至数据(LTD):

- PFD跟踪到达数据;

- 在接受其正常工作期间使用。

CDR支持自动或手动的控制器锁定模式。自动锁定模式中,根据LTR和LTD自动切换CDR模式,或使用“rx_freqlocked”信号来确定状态,‘1’表示CDR处于LTR模式,应用程序能够开始接收数据;‘0’表示CDR处于LTD模式,CDR不跟踪数据。手动模式需要通过控制信号来进行切换,如下表:

| rx_locktorefclk | rx_locktodata | CRU模式 |

|---|---|---|

| 1 | 0 | 跟踪参考时钟 |

| X | 1 | 跟踪数据 |

| 0 | 0 | 自动 |

如果需要较快的CDR锁定时间,则使用手动模式。

输出标志“rx_pll_rock”指示CDR锁定在输入参考时钟。

解串器与发送器串化器相似。

接收器PCS功能模块包含以下部分:

- 字对齐器;

- 去偏移FIFO(基本模式不支持);

- 速率匹配(时钟速率补偿)FIFO;

告辞。