数字IC设计基础

22 Jan 2020 2067字 7分 次 Digital IC Design打赏作者 CC BY 4.0 (除特别声明或转载文章外)

1 前言

2 数字IC设计流程

2.1 集成电路产业链:

| 集成电路设计公司(IC Design House) | 晶圆厂(fab) | 封测厂(Packaging&Testing) | 组装厂(Assembing) | 成品整机 |

|---|---|---|---|---|

| 算法,架构,前端,后端,仿真,流程,IP…… | 提供设计资源与技术支持,晶圆制造 | 晶圆切割,载板采购,硅片贴装,注塑,芯片成型,测试,包装…… | 辅料采购,PCBA焊接,测试,整机组装,整机测试,老化测试…… | |

| APPLE,高通,华为…… | 台积电,三星,中芯国际…… | 富士通,日月光…… |

国内著名的IC设计厂商:

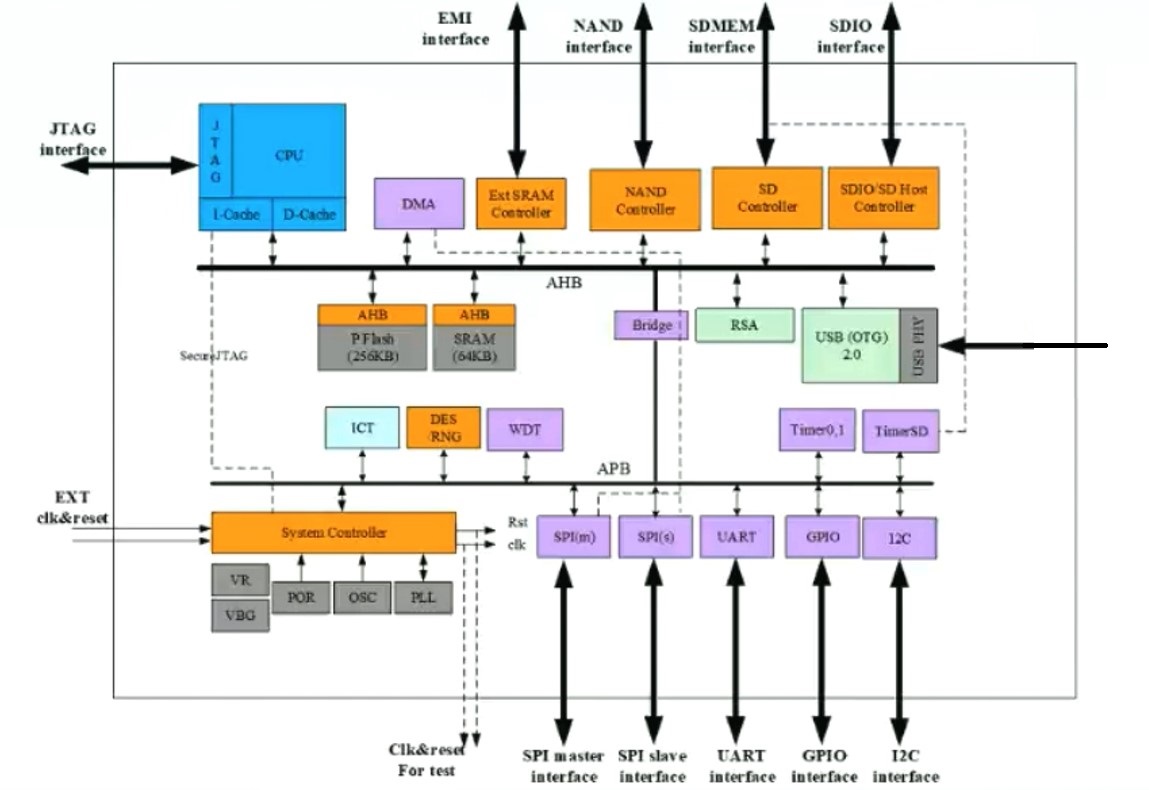

2.2 常见SoC芯片架构图

其中:

- CPU、DMA、还有一些通信接口等等做过单片机或者嵌入式的都知道;

- Ext SRAM:接口IP,外部可以连接SRAM存储器,用于程序的运行;

- Nand Flash Controller:接口IP,外接Nand Flash;

- SD Controller:接口IP,外接SD卡;

- SD Host:master接口,外接SD slave设备;

- AHB Pflash:片内存储体,Programming Flash存储体,类似PC系统盘;

- AHB SRAM:片内运存,类似PC内存;

- AHB-Brige-APB:AMBA2.0总线协议;

- System Controller:用于产生系统时钟和复位信号。

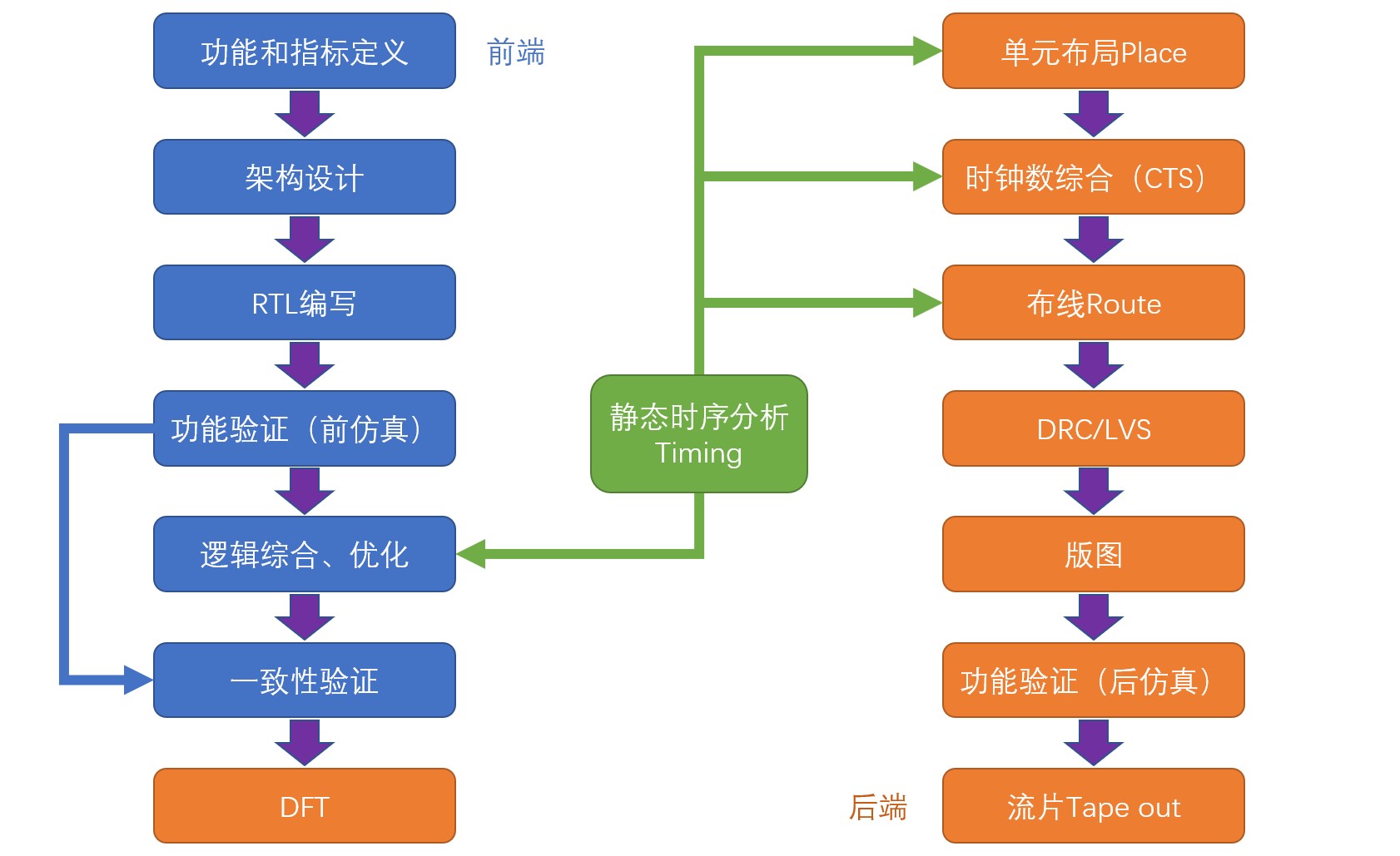

2.3 数字IC设计流程

| 确定项目需求 | 系统级设计 | 前端设计 | 后端设计 |

|---|---|---|---|

| 指定芯片具体指标 | 用系统建模语言对各个模块描述 | RTL设计、仿真、硬件原型验证、电路综合 | 版图设计、物理验证、后仿真等 |

具体流程:

2.4 数字IC设计指标

| 物理指标 | 性能指标 | 功能指标 |

|---|---|---|

| 制作工艺、裸片面积、封装 | 速度、功耗 | 接口描述、接口定义 |

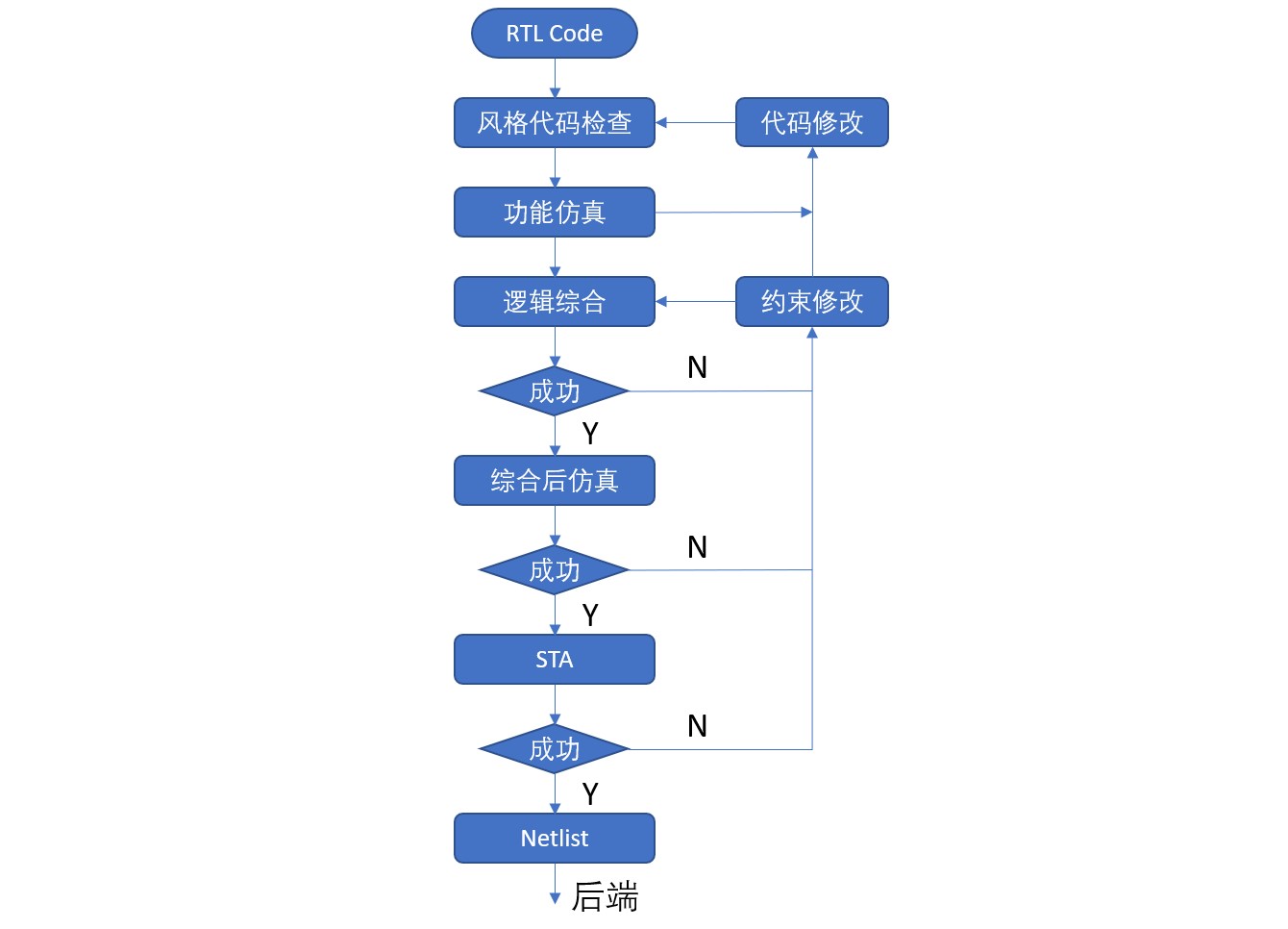

2.4 数字IC前端设计流程

3 数字电路基础

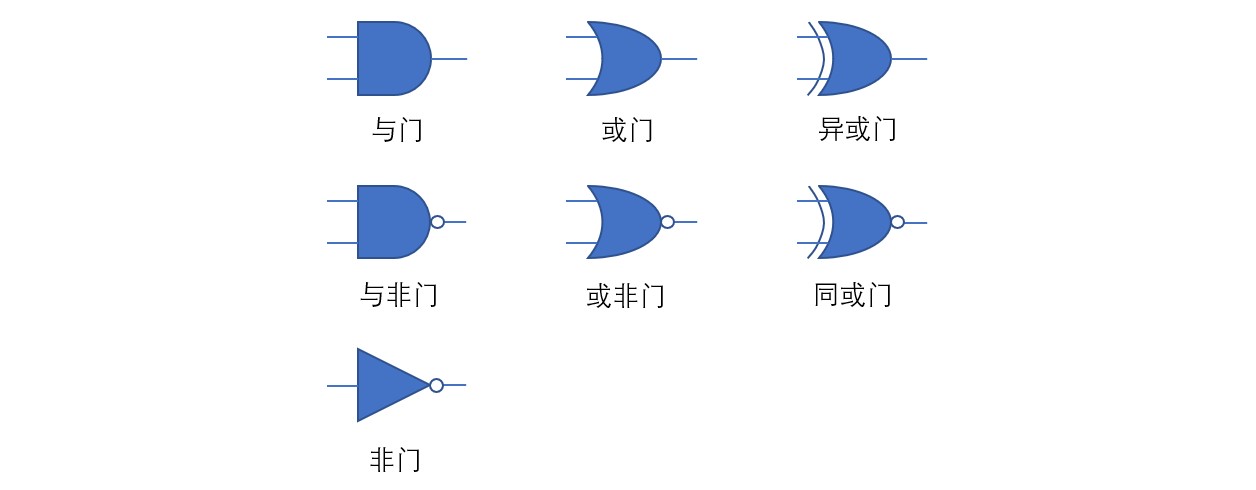

3.1 逻辑门

逻辑门国外流行符号:

3.2 CMOS器件

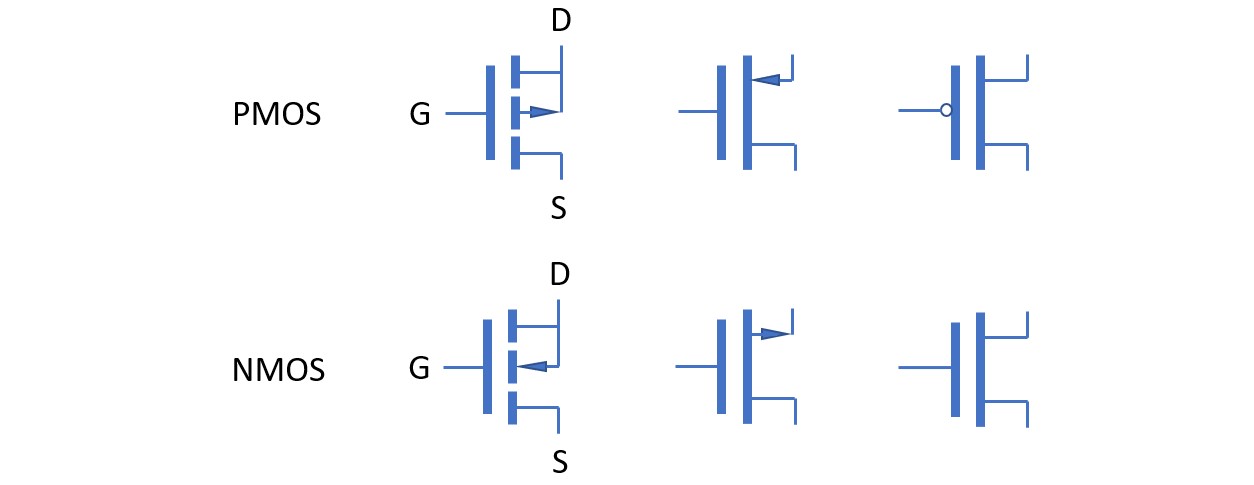

CMOS器件的符号,右邊是简化图:

其中PMOS的G极为低时导通,NMOS相反。PMOS衬底接电源,NMOS衬底接地。

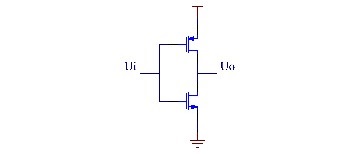

使用MOS管搭建反相器:

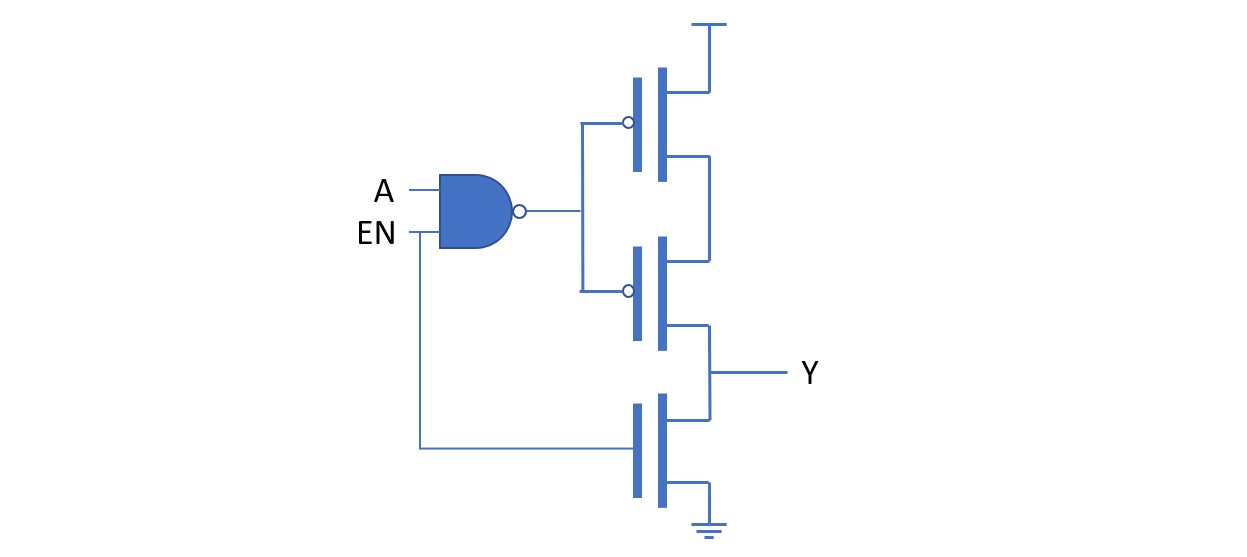

使用MOS管搭建三态非门:

使用MOS管搭建三态缓冲门:

使用MOS管搭建三态传输门:

将逻辑表达式转变为MOS电路的思路就是将有或的表达式都变成与和非,然后通过MOS与非门和MOS或非门以及MOS非门搭建出来。

例如:

Y = A · B + C

可以写成:

Y = ( (A · B)’ · C’ )’

(A · B)’用一個二輸入的与非门实现,C’用一个非门实现,最后把这两个结果用一个二输入的与非门得到Y。

而且与非门比或非门速度快。因为电子迁移率是空穴的2.5倍,而PMOS采用空穴导电,NMOS采用电子导电,所以相同尺寸下,PMOS充电时间长,比较最长路径的延时,与非门是两个PMOS并联,或非门是两个NMOS并联,因此与非门的速度更快。

另外,PMOS传输强1弱0,NMOS传输强0弱1,所以PMOS要负责输出1,NMOS负责输出0。如果反过来的话输出电压不能达到满摆幅,而且会向后影响,最终无法区分0或1。

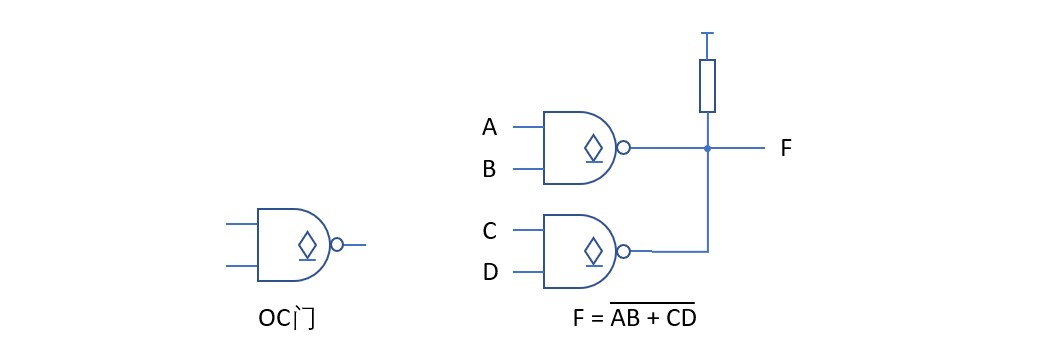

3.3 OC、OD门

集电极开路门(OC)因为负责输出的三极管的集电极啥都不接,所以叫集电极开路门。电路符号如图左侧所示:

漏极开路门(OD)与OC门类似。将三极管换成场效应管,

线与逻辑是两个或多个输出信号相连可以实现与的功能。在硬件上,要用 OC 门来实现(漏极或者集电极开路),为了防止因灌电流过大而烧坏OC门,应在OC门输出端接一上拉电阻(线或则是下拉电阻),如上图右侧。

3.4 数字电路功耗

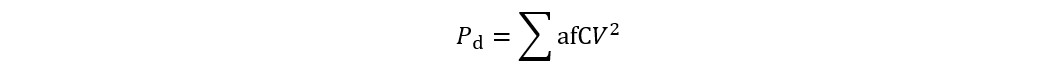

在RTL编码中考虑的功耗:

其中:

- Pd:电路个点的功耗总和。

- a:电路翻转次数;

- f:电路的工作频率;

- C:该点的电容;

- V:电压值。

其中负载电容和和工作电压是RTL设计无法改变的因素,在RTL级主要考虑尽量降低电路的翻转频率。

主要措施:

- 门控时钟;

- 增加使能信号,是的部分电路只有在需要工作时才工作;

- 对芯片的各个模块进行控制,在需要工作时才工作;

- 除了有用信号和时钟翻转会消耗功耗,组合逻辑产生的毛刺也会大量消耗功耗。但是,毛刺在设计中无法避免,因此只有尽量减少毛刺在电路中的传播,才可以减少功耗。即在设计中,尽量把产生毛刺的电路放在传播路径的最后,另外,可以使用一些减少毛刺的技术。

- 对于有限状态机,可以通过低功耗编码(减少每次翻转的位数)来减少电路的翻转。

CMOS反相器的功耗:

P = P_dynamic + P_static

其中:

P_dynamic = P_short + P_switch

P_static = P_leakage

其中:

- P_switch:电路翻转产生的动态功耗;

- P_short:P管和N管同时导通时的短路功耗,在“0”和“1”转换的过程中,P、N管会同时导通,产生一个由Vdd到Vss的窄脉冲电流,由此引起功耗;

- P_leakage:反偏PN结电流和MOS管的亚阈值电流引起的静态功耗。

告辞