VCS编译仿真操作

26 Jun 2020 3854字 13分 次 Digital IC Design打赏作者 CC BY 4.0 (除特别声明或转载文章外)

1 前言

以编译仿真AXI4_Interconnect为例,记录全过程。

- 开发环境:

- VCS 2016.06

- 操作系统:

- Ubuntu 18.04 LTS

2 前期准备

2.1 工程目录

首先建立工程目录,以AXI4_Interconnect为例:

- AXI4_Interconnect:

- cm:配置文件;

- com:编译之后的文件;

- data:仿真时要用的数据文件;

- doc:文档;

- sim:仿真之后的文件

- tb:Testbench文件和RTL文件;

将RTL文件放入对应文件夹,把Testbench文件放入“tb”文件夹;在“cm”文件夹中创建配置文件“xxx.cfg”,用来声明关系或不关心的文件。

2.2 脚本文件

在“AXI4_Interconnect”目录下还要在建立两个文件:“filelist.f”和“Makefile”。

其中,“filelist.f”文件中写入需要编译仿真的文件列表:

//源文件

../design/rtl/AXI_Arbiter_R.sv

../design/rtl/AXI_Arbiter_W.sv

../design/rtl/AXI_Master_Mux_R.sv

../design/rtl/AXI_Master_Mux_W.sv

../design/rtl/AXI_Slave_Mux_R.sv

../design/rtl/AXI_Slave_Mux_W.sv

../design/rtl/AXI_Interconnect.sv

//Testbench

./tb/AXI_Interconnect_TB.sv

./tb/AXI_Master.sv

./tb/AXI_Slave.sv

“Makefile”文件是编译仿真等的脚本文件,它指定了指令名称和相关的语句:

#===================================================================================

# Project Name: FIR

# Department: Xidian University

# Function Description: FIR仿真

#------------------------------------------------------------------------------

# Version Design Coding Simulata Review Rel data

# V1.0 Verdvana Verdvana Verdvana 2020-4-13

#-----------------------------------------------------------------------------------

# Version Modified History

# V1.0

#===================================================================================

.PHONY: com cov sim urg clean debug

#===================================================

# 定义

#===================================================

# 指定可执行文件名称

OUTPUT = AXI_Interconnect

# 宏定义

ALL_DEFINE = +define+DEFINE

POST_SIM_ON = +define+POST_SIM

# 指定时间单位和精度

TIME_DEF = -timescale=1ns/1ns

# 定制文件路径

#INC_DIR = +incdir+./rtl \

+incdir+./tb

# 代码覆盖率指令

CM = -cm line+cond+fsm+branch+tgl

CM_NAME = -cm_name ${OUTPUT}

CM_DIR = -cm_dir ./cm/${OUTPUT}.vdb

CM_LOG = -cm_log ./cm/cm.log

#CM_HIER = -cm_hier ./cm/cm_hier.cfg

# 后仿真库文件

#LIB_DIR =

#LIB_EXT = +libext+.v

LIB_FILE = -v lib_file ../synthesis/library/verilog/smic18.v

# 指定VPD文件名

VPD_NAME = +vpdfile+./sim/${OUTPUT}.vpd

# 编译命令

# 前仿真

VCS = vcs -full64 -cpp g++-4.8 -cc gcc-4.8 -LDFLAGS -Wl,-no-as-needed \

-sverilog +v2k \

${TIME_DEF} \

+rad \

-simprofile \

-debug_all \

+notimingcheck \

+nospecify \

+vcs+flush+all \

${CM} \

${CM_NAME} \

${CM_DIR} \

${CM_HIER} \

${ALL_DEFINE} \

${VPD_NAME} \

-o ./com/${OUTPUT} \

-l ./com/compile.log

# 仿真命令

SIM = ./com/${OUTPUT} \

${CM} ${CM_NAME} ${CM_DIR} ${CM_LOG}\

${VPD_NAME} \

-l ./sim/sim.log

#===================================================

# 执行

#===================================================

# 开始编译

com:

${VCS} -f filelist.f

# 开始仿真

sim:

${SIM}

# 显示覆盖率

cov:

dve -full64 -covdir ./cm/*.vdb &

# 生成覆盖率报告

urg:

urg -full64 -dir ./cm/*.vdb -format both

# Debug

debug:

dve -full64 -vpd ./sim/${OUTPUT}.vpd &

# Clean

clean:

rm -rf ./com/* ./sim/* \

./profileReport ./simprofile_dir \

./urgReport ./DVEfiles ./csrc \

./cm/*.vdb ./cm/cm.log \

profileReport.* *.key

命令的含义注释里基本都说明了。

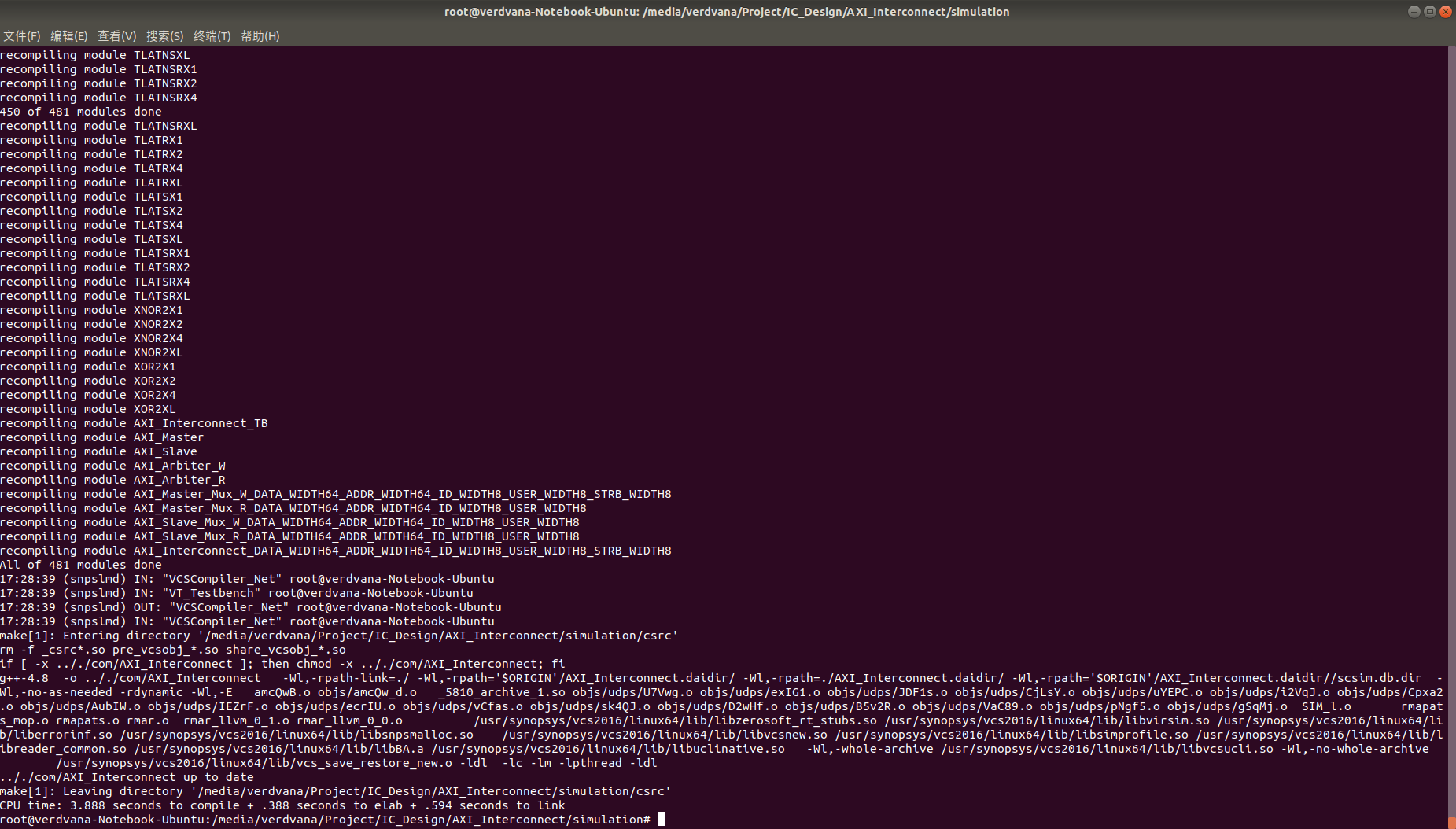

3 编译

在管理员模式下进入工程根目录(Makefile文件路径中),输入指令:

make com

编译通过之后结果如下:

编译成功之后“com”文件下会产生相应的文件和编译记录“compile.log”,另外还会在工程目录下产生“csrc”文件夹。

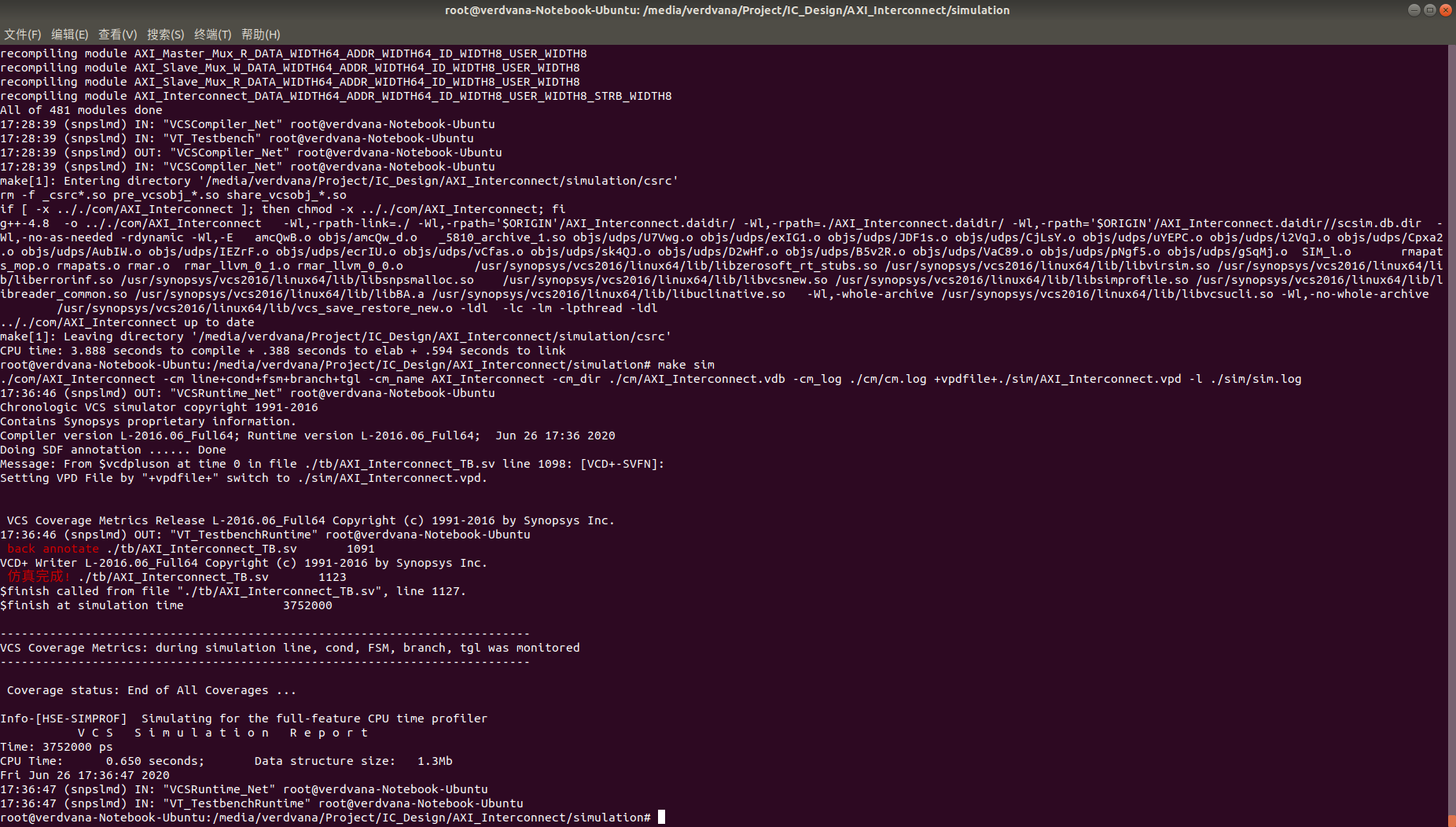

4 仿真

还是在工程目录下输入指令:

make sim

编译完成之后结果如下:

如果Testbench有打印的信息,则会打印在终端上。另外还会在工程目录中产生一系列文件。

4 Debug

还是在工程目录下输入指令:

make debug

启动V图形化的VCS,之后看波形的操作和ModelSim类似。

5 Clean

6 后仿真

7 Error解决

7.1 gcc-4.8: Command not found

Ubuntu 20.04自带的gcc版本不是编译所需的4.8,于是会报错:

所以需要安装4.8版本的gcc。输入如下命令安装:

sudo apt-get install gcc-4.8 g++-4.8

这时报错为:

按照提示说的添加其它发布源。输入如下指令打开源列表:

sudo gedit /etc/apt/sources.list

在末尾添加:

deb http://dk.archive.ubuntu.com/ubuntu/ xenial main

deb http://dk.archive.ubuntu.com/ubuntu/ xenial universe

保存并关闭,之后更新源:

sudo apt update

更新完之后再次输入如下指令安装gcc 4.8:

sudo apt-get install gcc-4.8 g++-4.8

这次应该能够安装成功了,安装好之后查看一下默认版本:

gcc --version

可以看到默认版本依然是自带的9.3.0:

把4.8版本的优先级设置为100:

sudo update-alternatives --install /usr/bin/gcc gcc /usr/bin/gcc-4.8 100

再次输入指令查看:

gcc --version

可以看到默认版本已经是想要的4.8了:

这时候再编译时能够发现这个问题被解决了。

告辞