1.前言

Intel收购Altera之后出了个Cyclone10系列,本着啥都要用最新的原则,做一个核心板玩玩。GX太高端,做个LP的就好。

- 开发环境:

- Alitium Designer 19.0.10

- 操作系统:

- Windows 10 Pro 1809

2.芯片选型

之前电赛(呸!研电赛只配叫PPT大赛/导师脱密项目大赛/创新大赛。校赛确实很操蛋,没有实物展示的都能那个三等奖,不过好在没啥用而且西北赛区的比赛中还是比较注重“电子”二字的,一些校赛时买来的平台改改例程就拿奖的,第一轮就给刷了,开心!)做了一块CycloneⅣ的核心板,采用的EP4CE10,只有10K的LE和46个Memory Block,很快就会不够用,所以这次选用有40K的LE的芯片。

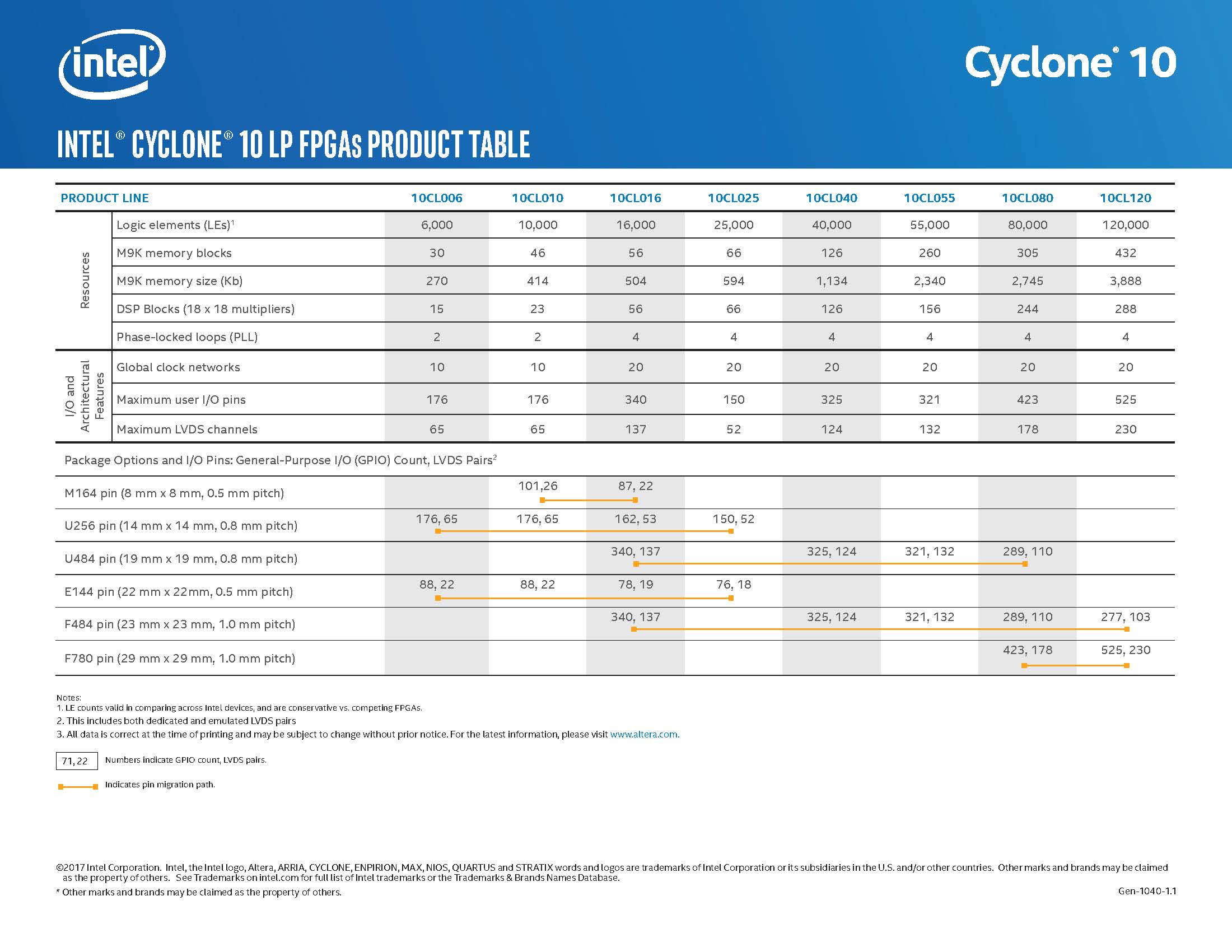

在Intel官网下载Cyclone10LP的产品列表,如下图:

可以看到40K个LE的芯片型号为“10CL040”,126个block的memory等等。有UBGA和FBGA两种封装,这两种封装区别在于引脚中心之间的距离:UBGA为0.8mm,FBGA为1.0mm。这里选用间UBGA封装。

3.添加封装

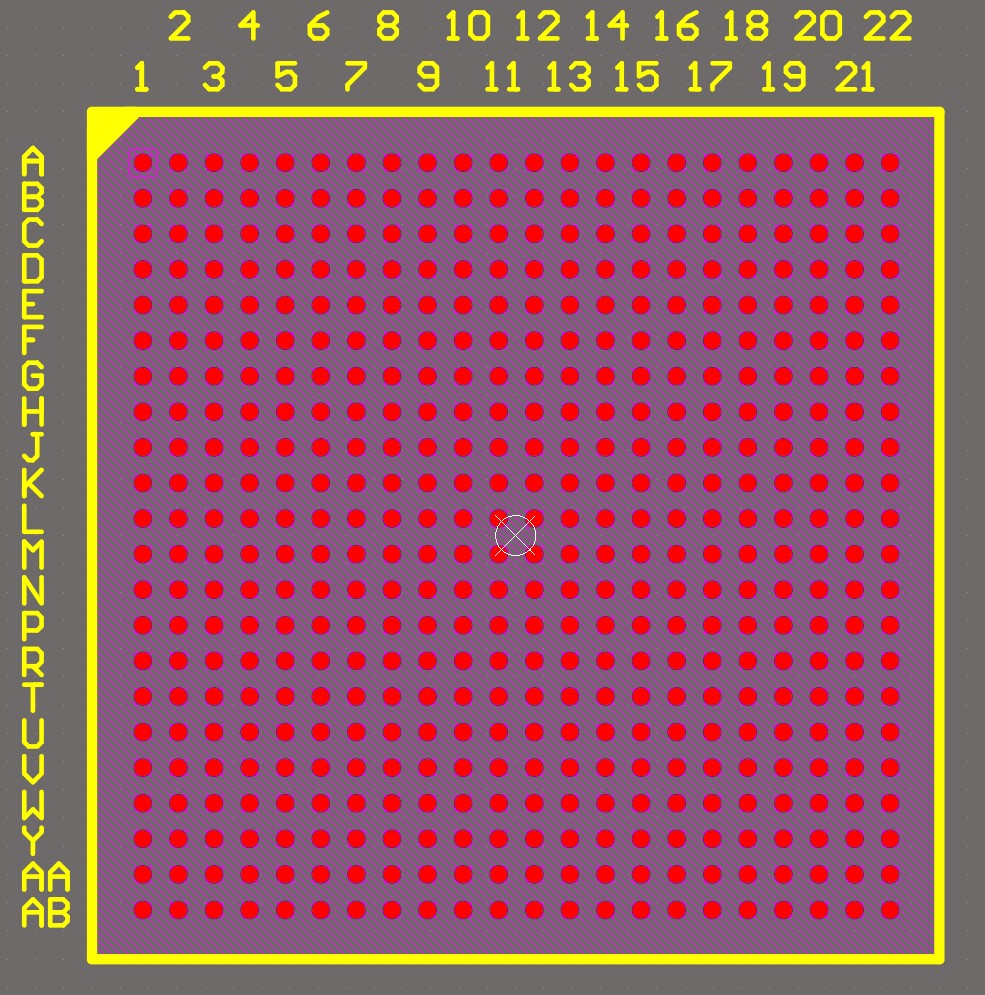

打开Altium Designer,新建核心板工程,在工程下新建PCB封装库。按照手册放置焊盘。焊盘直径0.4mm,间距0.8mm,组成22×22阵列。Designator如下图:

最后在丝印层按照芯片尺寸19mm×19mm画上边框就🆗,如果想画3D模型可以通过放置球形和方形的3D模型组合成芯片的样子。如图:

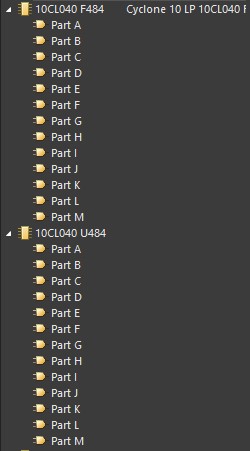

然后就是添加原理图库。在工程下新建原理图库,分Part添加10CL040的原理图。484个脚添加完AD200都出来了,所以可以去Intel官网的相关页面下载原理图库。下载到的是OrCAD对应格式的,AD可以直接转换。

转换好格式后稍作修改,把刚刚的封装添加进去,就可以用了。

4.原理图设计

4.1 电源设计

上一次做CycloneIV核心板用的都是AMS1117的电源芯片,被各种吐槽,这次参考一下Intel官方开发板的电源。去官网相关页面下载英特尔Cyclone10LP FPGA评估主板原理图。

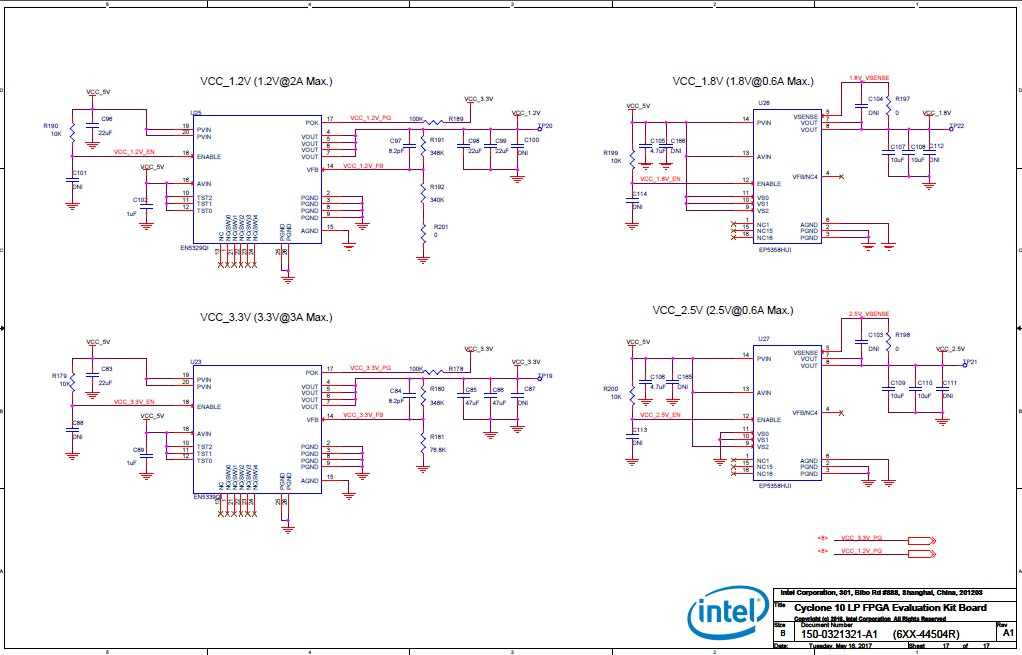

最后一页就是电源部分原理图:

可以看到输入电压为5V,然后产生3.3V、2.5V、1.8V和1.2V四种电源。1.8V是给HyperRAM用的,不打算用这玩意就不管它了。

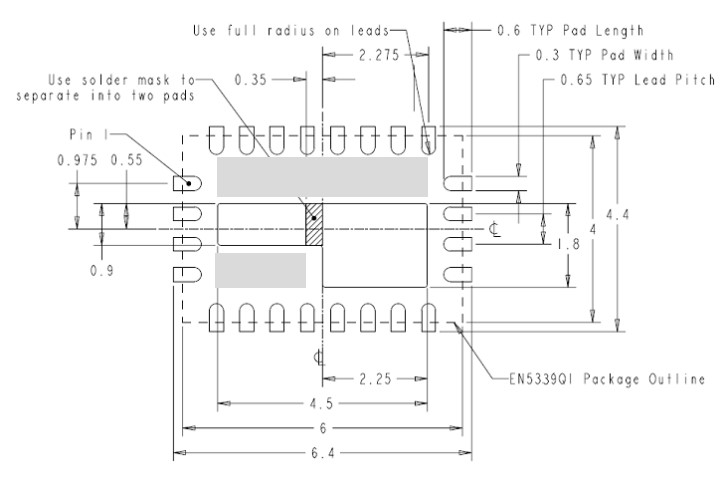

5V转3.3V用了一个EN5339QI芯片,去官网下载数据手册可以发现这东西封装很奇怪:

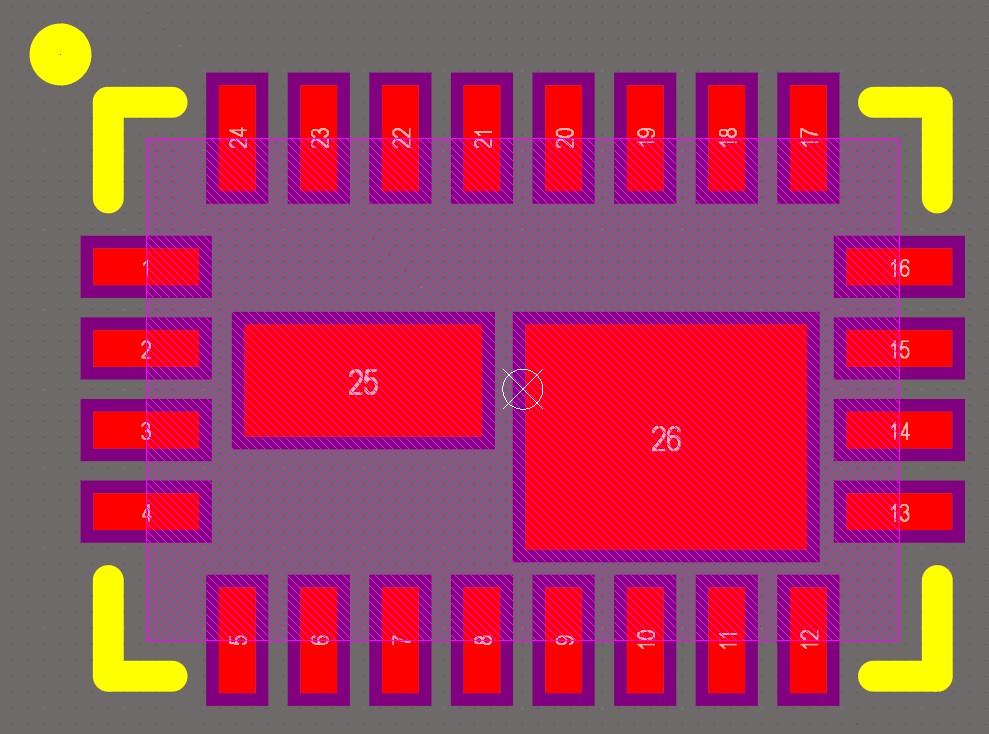

长宽不一致、背面焊盘不对称的QFN24封装,所以只能自己画:

原理图库也要添加。好消息是5V转1.2V的芯片EN5329QI的引脚和它完全兼容,只是电流不同,可以直接用。

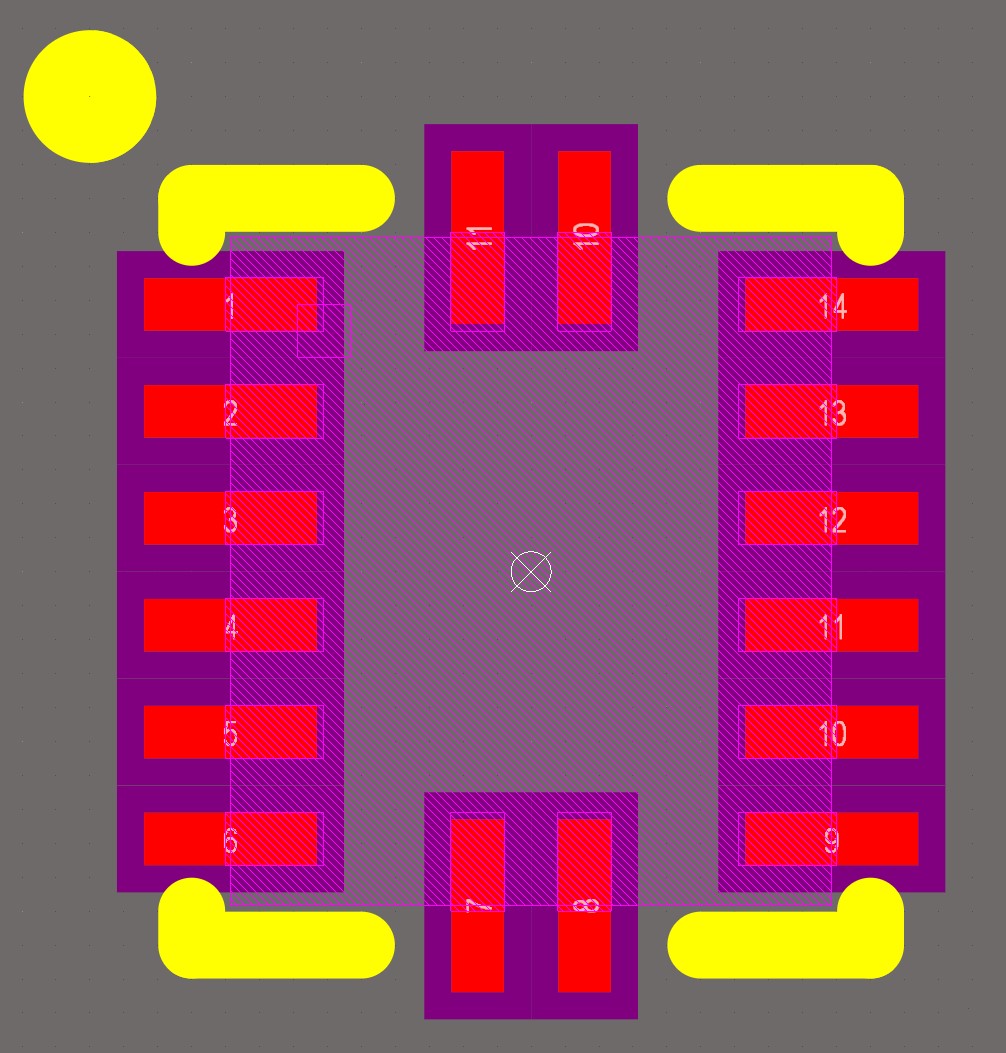

再看5V转2.5V芯片,用了EP5358HUI,封装也挺有意思,画就完了。

同样根据数据手册再画好原理图库,匹配好封装,就可以用了。

我这里选用Mini USB接口作为电源输入,自锁开关当开关,并且串了一个2A的保险。既然用了USB当电源,就顺带添加了USB转TTL芯片。原理图如图所示:

4.4 芯片及配置设计

把之前创建的原理图库里的芯片原理图拽出来放进工程的原理图文件里,一个A4页面放不下,我用了三页。

4.3 时钟设计

10CL040有16个时钟输入或8对差分时钟输入,官方开发板上时钟挺多,用了Si5351A时钟芯片,这里只需要一个50MHz的时钟输入,所以挂一个50MHz有源晶振就行。其他时钟引脚可以作为外部时钟输入。原理图如图所示:

告辞。