1 前言

之前学习过凡亿郑振宇老师的《Altium 4层核心板全程PCB实战视频教程(Fly-by菊花链拓扑)》,里面提了一下阻抗计算,通过阻抗计算来确定走线宽度。

- 开发环境:

- Polar Si9000

- 操作系统:

- Windows 10 Pro 1903

2 PCB层叠

郑振宇老师的《Altium Designer 17 电子设计速成实战宝典》一书中将2、4、6、8层板的叠层结构和每种结构的优缺点都讲得很明白,并且给出了不同层数的推荐结构。

3 PCB的阻抗计算

3.1 为什么要计算阻抗

当电压电流在传输线传播的时候,如果特性阻抗不一致就会造成所谓的信号反射现象等等。在信号完整性领域里,比如反射、串扰、电源平面切割等问题都可以归类为阻抗不连续问题,因此匹配的重要性在此展现出来。

3.2 常见阻抗模型

这里使用Polar Si9000进行阻抗计算,在计算之前需要认识常见的阻抗计算模型,常见的阻抗模型有特性阻抗、差分阻抗、共面性阻抗。阻抗模型又细分为如下几类:

- 外层特性阻抗模型

- 内层特性阻抗模型

- 外层差分阻抗模型

- 内层差分阻抗模型

- 共面性阻抗模型

- 外层共面特性阻抗

- 内层共面特性阻抗

- 外层共面差分阻抗

- 内层共面差分阻抗

3.3 阻抗计算

阻抗计算的必要条件:

- 板厚;

- 层数(信号层数、电源层数);

- 板材;

- 表面工艺;

- 阻抗值;

- 阻抗公差;

- 铜厚。

影响阻抗的因素:

- 介质厚度;

- 介电常数;

- 铜厚;

- 线宽;

- 阻焊厚度。

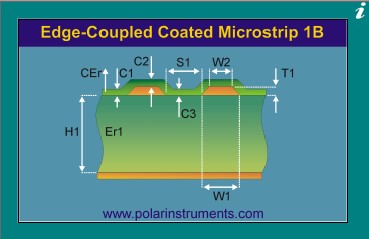

如下图所示:

其中:

- H1:介质的厚度(PP片或者板材,不包括铜厚);

- Er1:PP片或者板材的介电常数,多种PP片或板材压合一起时取平均值;

- W1:阻抗线下线宽;

- W2:阻抗线上线宽;

- T1:成品铜厚;

- Cer:绿油的介电常数(3.3);

- C1:基材的绿油厚度(一般按照0.8mil);

- C2:铜皮或者走线上的绿油厚度(一般按照0.5mil);

- Zo:计算出来的阻抗理论值。

一般来说上下线宽存在如下关系(W0为设计线宽,S0为设计线距·):

| 基铜厚 | 上线宽(mil) | 下线宽(mil) | 线距(mil) |

|---|---|---|---|

| 内层 18um | W0-0.1 | W0 | S0 |

| 内层 35um | W0-0.4 | W0 | S0 |

| 内层 70um | W0-1.2 | W0 | S0 |

| 负片 42um | W0-0.4 | W0+0.4 | S0-0.4 |

| 负片 48um | W0-0.5 | W0+0.5 | S0-0.5 |

| 负片 65um | W0-0.8 | W0+0.8 | S0-0.8 |

| 外层 12um | W0-0.6 | W0+0.6 | S0-0.6 |

| 外层 18um | W0-0.6 | W0+0.7 | S0-0.7 |

| 外层 35um | W0-0.7 | W0+0.9 | S0-0.9 |

| 外层 12um(全板镀金工艺) | W0-1.2 | W0 | S0 |

| 外层 18um(全板镀金工艺) | W0-1.2 | W0 | S0 |

| 外层 35um(全板镀金工艺) | W0-2.0 | W0 | S0 |

普通的FR-4板材一般有:生益,建滔,联茂等板材供应商。生益FR-4及同等材料芯板可以根据板厚来划分,下表列出了详细的厚度参数及介电常数:

| 类别 | 板芯(mil) | 2.0 | 3.0 | 4.0 | 4.33 | 5.1 | 5.9 | 7.0 | 8.27 | 10.0 | 14.5 | 20.0 | 28 | ≥31.5 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| (mm) | 0.051 | 0.075 | 0.102 | 0.11 | 0.13 | 0.15 | 0.18 | 0.21 | 0.25 | 0.36 | 0.51 | 0.71 | ≥0.8 | |

| Tg≤170 | 介电常数 | 3.6 | 3.65 | 3.95 | 无 | 3.95 | 3.65 | 4.2 | 3.95 | 3.95 | 4.2 | 4.1 | 4.2 | 4.2 |

| IT180AS1000-2 | 介电常数 | 3.9 | 3.95 | 4.25 | 4.0 | 4.25 | 3.95 | 4.5 | 4.25 | 4.25 | 4.5 | 4.4 | 4.5 | 4.5 |

半固化片(PP片),一般包括:106、1080、2116、7628等,其厚度为0.04mm、0.06mm、0.11mm、0.19mm,下表列出了常见PP片的厚度参数及介电常数:

| 类别 | PP片 | 106 | 1080 | 3313 | 2116 | 7628 |

|---|---|---|---|---|---|---|

| Tg≤170 | 理论实际厚度(mm) | 0.0513 | 0.0773 | 0.1034 | 0.1185 | 0.1951 |

| 介电常数 | 3.6 | 3.65 | 3.85 | 3.95 | 4.2 | |

| IT180AS1000-2 | 理论实际厚度(mm) | 0.0511 | 0.07727 | 0.0987 | 0.1174 | 0.1933 |

| 介电常数 | 3.9 | 3.95 | 4.15 | 4.25 | 4.5 |

对于Rogers板材,Rogers4350 0.1mm板材介电常数为3.36,其他Rogers4350板材介电常数为3.48.Rogers4003板材介电常数为3.38,Rogers4403半固化片介电常数为3.17。

每个多层板都是由芯板和半固化片通过压合而成的,计算层叠结构的时候通常要把芯板和PP片叠在一起,组成板子厚度,比如一个芯板+两张PP片叠加“芯片+106+2116”,那么他的理论厚度就是0.25mm+0.0513mm+0.1185mm=0.4198mm。但需注意以下几点:

- 一般不允许4张或4张以上PP叠放在一起,因为压合时泳衣产生滑板现象;

- 7628的PP一般不允许放在外层,因为7628表面比较粗糙,会影响板子外观;

- 3张1080也不允许放在外层,因为压合时也容易产生滑板现象;

- CORE一般选择大于0.11mm的,六层的一般2块芯板,8层得到三块芯板。

由于铜厚,理论厚度和实测厚度有一定误差,差额的计算如以下公式:

实测厚度 = 理论厚度 - 铜厚1(1-X1) - 铜厚2(1-X2)

其中:

- X表示残铜率,表层X取1,光板X取0;

- 电源地平面残铜率一般为取值70%,信号层残铜率一般取值为23%。

残铜率是指板平面上有铜的面积和整板面积之比。比如张没有加工的原材料残铜率就是100%,蚀刻成光板时就是0%。

3.4 计算实例

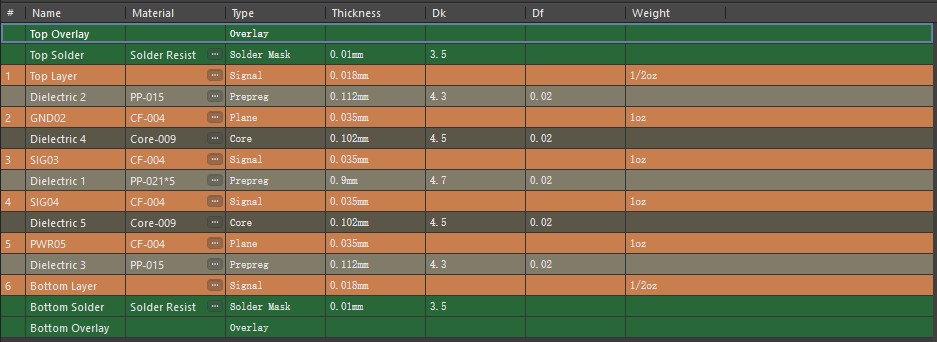

层叠要求:板厚:1.6mm;板材:FR-4;层数:6层;铜厚:内层1Oz,表层:0.5Oz。

根据板芯和PP片常见厚度参数组合,并根据叠层厚度要求可以堆叠如下层压结构:

由上图可以算出板子总厚度 = 0.01mm+0.018mm+0.112mm+0.035mm+0.102mm+0.035mm+0.9mm+0.035mm+0.102mm+0.035mm+0.112mm+0.018mm+0.01mm = 1.524mm。

打开Si9000软件,选择需要计算阻抗的阻抗模型,计算表层50欧姆单线阻抗线宽。根据压合层叠数据,填入相关数据,点击计算:

计算出走线宽度为8.3mil,这个是计算出比较粗的走线,有时候会基于走线难度准许阻抗存在一定的误差,所以可以根据计算得出的走线线宽来稍微调整,比如调整线宽为6.6mil,阻抗为56.65Ω:

告辞。